| OCR Text |

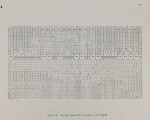

Show 47 Column 234 1 1--1 2 I CPUll Latcb R 3 ICPUrl 04 I 1-PW5 I 1-R- 6 I o-P- 7 - S--- 8 - R--- ICPUll lePUrl IINV I S - 1 I P - 0 I 1 - + I Figure 6: !he Use of Standard PPL Cells in a Non-Standard Way signal to a set of registers. Column 1 contains enabling signals for register operation. Note that while column 1 and column 4 look much aliKe, they are very differet. Column 4 contains an inverter (labeled "INV") for -driving t·he bus .and two- column loads ("CPU1" and "CPUr"). Column 1 contains only two column loads and no inverter. Column 4 has meaning in the SLA context while column 1 has not. Row 4 tells us that when column 1 is true (i.e. the right wire in the column is pulled low) and when the bus is true in the standard SLA sense (true -LOW), the latch will De set, thereDy loading the true state of the bus into the register bit. The cell labeled "P" denotes a row load. Row 5 tells us that when column 1 is true (i.e. the right wire in the column is pulled low) and when the bus is false in the standard SLA sense, the latch will be reset, thereby loading the false state of the bus into the register bit. Row 6 indicates that when column 1 is false (Le. the left wire in the col is puled low) and wnen the latch is tue (indicated by t!:1e 1 in colurcn 3), the bus will be driven from this register bit. |