| OCR Text |

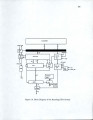

Show 99 and D bits. Finally, Ack will go low indicating that the adder is reset and is ready for a new computation. Figure 5.5 shows how to build a 4 bit CCS adder[4] . When Req goes high, it allows each stage to compute the sum and the carries. When all stages are done, the output C element fires raising the Ack signal. In response, Req goes low, thus clearing the carry bits. When all stages have cleared, the C element will fire making Ack go low. Although a CCS adder could be built using DCFL by incorporating the Req signal into the logic equations, the precharged circuits discussed in Chapter 3 provide a natural and elegant way of implementing this adder with the precharged signal acting as the Req signal. When the precharge signal is high all the carry bits are cleared and when the precharge signal is low, the computation starts (note that the sense is now reversed). In Chapter 3, the design of a 32 bit adder was discussed using the propagate signal and SPICE results tabulated. Although one could adopt a similar approach for building a 25 bit adder, things could be speeded up by building a precharged carry skip CCS adder. The basic idea is that we split A [ 0:3 ] B [0 :3] ACK AO BO Al Bl A2 B 2 SUMO SUMl SUM2 SUM3 SUM[0:3 ] Figure 5.5. Four Bit CCS Adder |