| OCR Text |

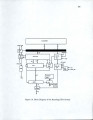

Show 18 is a reflection of the number of 1s in the input [11]. In this chapter all delays are measured in terms of CSA delays in order to serve as a basis of comparison. The NOR gate realization of the full adder is shown in Figure 2.2. Since we are interested in a GaAs implementation with DCFL logic family (see Chapter 3), only a NOR realization is shown. 2.4.2 ( 4,2) Counter This cell was first described in [36]. It takes four inputs and produces two outputs- one of the same weight and the other of a higher weight as shown in Figure 2.3. It also shows how one can build a ( 4,2) counter out of two CSAs. Thus, a ( 4,2) cell has five inputs and three outputs (including the side carries). This raises the possibility of implementing the ( 4,2) counter directly from the truth table. However, an attempt to do that by using a five variable K-map shows that the sum does not get minimized (like the sum in the full adder). There are 16 product terms (each having 5 literals) and hence a two level realization using NOR gates is ruled out because of the huge fan in. A two level realization would have made a significant difference in a ( 4,2) counter based architecture (to be discussed later). However, implementing it with two CSAs is efficient and gives us a metric to compare with other architectures. 2.5 Array Multipliers The simplest way to build a parallel multiplier is to build an array multiplier. A 4 x 4 multiplier is shown in Figure 2.4. It can be very easily extended to 24 x 24. A layout o£ an 8 x 8 multiplier done using ACME shows that it occupies an area of 63 x 24 PPL [21] cells. By extrapolation a 24 x 24 multiplier would occupy 207 x 72 PPL cells (2.8mm x 2mm). This assumes a half adder can be custom designed that occupies only 2 PPL cells. Although very area efficient, it is also the slowest of all schemes. It has a latency of 23 CSAs. |