| OCR Text |

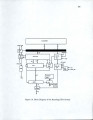

Show 85 delay between the rising edge of r2 and the generation of 11. The entry a2_2_11_1 shows the delay between the rising edge of ack2( ack1) and the time when 11 goes low. The entry a2_2_l1_2 shows the corresponding delay measured from the falling edge of ack2( ack1). Thus, in the worst case, we have about 300ps of margin. This can be extended by enabling the variable delay lines. Right now, one of the delay elements on the ack1 and ack2 lines is already enabled. The table entry tde1ay gives the time between the request signal to the generation of the acknowledge signal in the worst case. This gives the total delay for this stage. Finally, margin shows the bundling margin in the worst case. Note that delay measurements for l1 is the only one shown. The signal 12 is identical to 11 and the results are expected to be the same. 4.5.2 Simulating the Accumulator Control The control unit for stage-2 is quite similar to the control unit for stage-1. Also since ACME to SPICE netlist was causing a lot of problems, it was decided to better utilize the resources for simulating crucial units. These were the stage-1 and the accumulator control units. Also as we shall see, the accumulator control becomes the limiting factor and we can do without an exact knowledge of the delay for stage-2. In a separate simulation, the accumulator datapath was simulated with the routing capacitance (because of the right shift) taken into account. This delay was found to be about Ins in the worst case. Thus the control upit was going to be the bottleneck and it was simulated as a stand alone unit. Of course, extra capacitance on the latch signals as well as the request and acknowledge lines were added for accuracy. The results of the simulation are tabulated in Table 4.2. It would be helpful to refer to Figure 4.6 to get a better feel for the circuit. Since we have two latches here, one for the ( 4,2) counter stage and the other for the slave |