| OCR Text |

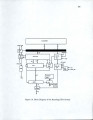

Show 98 in the worst case as compared to O(n) for a ripple carry scheme. However, this approach would be quite expensive in terms of area (especially important in GaAs) and its design would be quite complex with the DCFL restrictions on fanin and fanout. A ripple carry on the other hand has a very regular structure, well suited for VLSI. Another noteworthy feature about ripple carry adders is that only in the worst case, which could be rare, do they take O(n) time. It has been shown by [5] that the average time is only O(log n). Thus implementing a ripple carry adder that can detect when it is done seems to be a good compromise on speed and area. Such an adder indeed exists and is called a Carry Completion Sensing ( CCS) adder [17]. The truth table, taken from [4], for this kind of circuit is shown in Table 5.2. Instead of the usual carry into the next stage, this adder has a carry and a do not carry signal going into the next stage. This adder uses a four-phase signalling protocol. When the Req signal goes high, the adder begins computing. When the adder is done, all the carry and do not carry bits would be set or reset. This will make the adder raise its Ack signal. In response, Req will go low, resetting the C Table 5.2. Truth Table for CCS Addition En Cin Din AB Sum Cout Dout 1 0 0 00 X 0 1 1 0 0 01 X 0 0 1 0 0 10 X 0 1 1 0 0 11 X 1 0 1 0 1 00 0 0 1 1 0 1 01 1 0 1 1 0 1 11 0 1 0 1 1 0 00 1 0 1 1 1 0 01 0 1 0 1 1 0 10 0 1 0 1 1 0 11 1 1 0 1 1 1 XX X X X 0 X X XX X 0 0 |