| OCR Text |

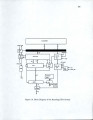

Show 82 • ACME does not put node names on the CIF which is a major problem. Considerable hand fixing of the .ckt file produced by ACME was required. Also in absence of an accurate capacitance estimate, the results noted in the following sections are only approximations. Unless explicitly stated, all SPICE figures have been obtained under typical-typical ( tt) process and 25°C. All simulations were done with a Vdd of 2V and a back gating voltage of 0.6V which is what Vitesse recommends. Also these simulations are by no means exhaustive and were done only to get an estimate of the delay times. 4.5.1 Simulation of Stage-1 There are two datapaths here as shown in Figure 4.8. One involves a NOR gate, wiring capacitance, inverters, ( 4,2) counter with built in Earle latch followed by an inverting superbuffer. This handles the multiplier bits y0,yl,y2,y3. The other one involves a NOR gate , full adder followed by another full adder with built in Earle latch. This handles y4,y5,y6,y7. After SPICE simulations it was found that the former datapath was the slower one, as was expected, and hence it was used in conjunction with the stage-1 control unit to get worst case results. The actual circuit used for SPICE simulations are shown in Figure 4.9. It would also be helpful to refer to Figure 4.4. Note the absence of hierarchy which was necessitated because of an ACME bug alluded to earlier. This is one bit slice of the multiplier. A single bit slice was taken to be the representative of all the bit slices in this stage. This is a reasonable assumption since all other bit slices are identical and are operating concurrently. Additional load capacitances were added onto the multiplier, multiplicand, latch signals, request and acknowledge lines to model the actual situation accurately. The capacitance values were obtained from the completed layout shown in Figure 4.8. The data obtained from SPICE simulations are shown in Table 4.1. |