| OCR Text |

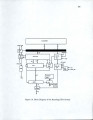

Show 79 somewhat. However, we are not ready to accept new data into the accumulator until the slave latch has latched the results of the previous iteration; hence the need for a C element. One final note is that after the third iteration, we can not accept new data into the accumulator till the CPA stage is done; hence the need for the 3 input XOR, which can be efficiently implemented with a full adder since the sum output of a full adder is the XOR of three inputs. 4.4.3.4 Functional Simulation The ACME layout of the whole 8 X 24 multiplier together with the control unit is shown in Figure 4.8. The whole circuit was functionally simulated by writing a .ppl file from the circuit and using SIMPPL to simulate the extracted netlist. The circuit was found to be fully functional for a wide range of test vectors. The test vectors typically used included, multiplying with zero, unity, both the operands being their max values, operands with alternating Os and ls, etc. 4.5 SPICE Simulations Since this is a self-timed design, we must do a detailed SPICE analysis to determine if the various bundling constraints are met. In this section, we look at the SPICE results for the three stages in the pipeline. It is also important to document the various bugs and problems that beset ACME at present in going from a design to a SPICE netlist. This would help in future bug fixes and will help place the SPICE results in their proper perspective. • The capacitance values on the internal nodes and outputs of the leaf cells was three-four times higher than those extracted from COMPASS. Finally, after experimenting with the vgaaslO process file, these numbers were corrected and are now slightly lower than those obtained from COMPASS. |