| OCR Text |

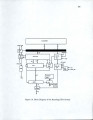

Show 77 transition signalling environment. However unlike stage-1 datapath where we had AND gates and wiring followed by the ( 4,2) counter, here we have a ( 4,2) counter with very little wiring. Thus, it is expected that the control circuitry would be the limiting factor rather than the datapath. However, we can speed up the control path somewhat by removing the sym_delay block from the ack signals if we could ensure that the bundling constraint is met by a sufficient margin. We can use a smaller delay in the path of the latching signal since the datapath is simpler and faster. We could do with just a full adder instead of a ( 4,2) counter. We could also remove the variable delay line if we could ensure that the bundling constraint would be met by a sufficient margin. 4.4.3.3 Accumulator Control Design As expected, the design of this stage was trickier than the other two. Refer to Figure 4.6 . The block basic_ctl refers to the control structure required for latching and is identical to Figure 4.4 except for the use of variable delay lines. Two such blocks are required because one is for the ( 4,2) counter stage and the other is for the slave latch used to prevent feed through, as discussed earlier. We also have a three output toggle for counting the number of iterations, whose circuit is shown in Figure 4. 7. As can be seen from the Figure 4. 7, the delay between the third firing of in and the next firing of in is considerably greater than the firing of the third output of the toggle and the fourth output which feeds back to the input through an XOR gate. Thus, under the circumstances this is a safe design. Also, note that the toggle3 block gets fired concurrently with the firing of the slave latch. The slave latch is required only for storing the results of the previous iteration. We can signal to the CPA stage as soon as the ( 4,2) counter stage is done with the third iteration. This technique thus helps speedup the accumulator |