| OCR Text |

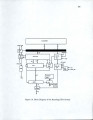

Show 71 5. Since presently functional simulation can not be done directly in ACME, SIMPPL has been used. SIMPPL requires the creation of a functional simulation model which must be entered in the SIMPPL database. The new cell also has to be entered into the TILER database. The following new cells have been entered into the database as part of the design process: 1. A two-level version of a full-adder. 2. An Earle latched version of the full-adder. 3. An Earle latched ( 4,2) counter. 4. A buffered Earle latched ( 4,2) counter. 5. An Earle latched ( 4,2) counter with two of the inputs coming from below. 6. A buffered Earle latch. 7. A two-level XOR gate with buffered output. 8. A precharged version of the full adder. An important consideration while designing the partial array is the width which is proportional to the size of the multiplicand. The width of each bit slice should be kept narrow, otherwise the circuit becomes very big. The routing here is more complicated as compared to the usual array multiplier because we have to route the output of one row of the 4-2 adder stage through the next sub-array and onto the next 4-2 adder stage, as is shown in Figure 2.10. Also these wires have to be aligned so that they get added to the right pair of bits. The full-adder in ACME is two PPL cells wide. If we take the routing also into consideration then the width of each bit slice becomes 4 PPL cells wide. Now, a (4,2) counter, as we have seen |