| OCR Text |

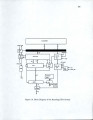

Show 68 4.4 Design Considerations The block diagram implementation of the PAA architecture is shown in Fig-ure 2.18 As can be seen from the figure, the approach is based on Sutherland's micropipelines [37] using bundled data path. The ACME implementation is done using the 1.0ftm cell library in ACME which has been designed using the Vitesse l.Oftm Self-Aligned GaAs process. In the next two subsections the design of the datapath and the control logic design will be described separately. 4.4.1 Reducing Latch Delays Since we are implementing a pipelined iterative multiplier we are usirig many latches. However, if care is not taken in minimizing these latch delays, the overhead incurred would be severe. In this subsection we look at a way of reducing this overhead. The Earle latch is one such circuit that has virtually no overhead and can be used for pipelined systems [8]. In Figure 4.1 (a) we have a logic function that we wish to latch. We can do this without incurring any overhead as shown in Figure 4.1(b) . The latch is transparent when Cis low and opaque when Cis high. However, this circuit has a serious problem. Consider the case when the output of the circuit is meant to be a 0 and the clock has just gone to 1. For a brief while Cbar will also be a 1 thus forcing the output Y to a 1 which is now fed back. Thus when Cbar will finally go to 0 an erroneous value of 1 would have been latched. To prevent this the circuit can be modified as in Figure 4.1( c) provided there is a suitable hold time. However, this means adding extra circuitry, which in the case of a CSA, will be quite large. A way of avoiding all this overhead is by ensuring that Cis delayed by at least Cbar· This can be done as shown in Figure 4.1(d). Though this eliminates the malfunction there will be a glitch on the output to a 1, i.e., if the latched value was a 0 and the new value is also a 0 then the output |