| OCR Text |

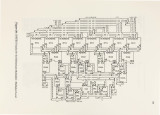

Show 81 Tile set NMOS40 SCMOS MEMORY3 Number of Tiles 37 42 23 Size of TDL File (bytes) 67980 112971 69106 Compile time of TDL File (seconds) 132 101 134 Size of Tileset File (bytes) 148198 362932 189738 Load Time of Tileset File (seconds) 48 55 41 Table 5: Comparison of Tile set Storage Methods be subdivided into row or column stacks of rectangles only. Since windows and panes are restricted to the rectangular realm, there is no such thing as, for instance, a toroidal window; that is, a window with a hole through which another window may be visible. This is what is implied by, for example, a hexagonal grid holding RAM tiles needing to be surrounded by and connected to a rectangular grid containing bussing and control tiles. The solution that looks most promising is to create a common interface grid (most likely at the micron size level) which will reside in several panes in the frame. Other grids will have their own pane, but the interface grid is "sliced up" as needed to satisfy the rectangular stacking constraint. Moving the view of the grid planes will then require "on-the-fly" reconfiguring of the panes in the frame, which is a very difficult and computa-tionally expensive proposition. Despite these obstacles, grid interfacing is an important enough component of the Structured Tiling methodology to justify devoting the required time and energy to realize and make efficient its implementation. At the present time, there is a way to construct circuits using two different tilesets, where the second one was designed to be "compatible" with the first. The MEMORY3 tileset is a CMOS tileset consisting of RAM tiles and amplifier tiles that have a denser wiring grid than the SCMOS tileset and grid. However, MEMORY3 also has special interface tiles that allow a memory array to be embedded in the SCMOS grid. (See [7].) Figure 29 shows an example of this. The tiles displayed with the characters M, R, Y, y, N, v, C, c, and the corners all belong to the MEMORY3 tileset; the rest belong to the SCMOS tileset. The COMPATIBLE-TILESETS instance variable of the grid links these two tilesets, and the compatible edge concept ensures that the tiles interface in the way intended. This feature was used to great advantage in the ATQ, which uses two memory arrays of 128 bytes each, plus one array of 16 bytes. |