| OCR Text |

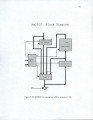

Show 22 input ports have the type in, output ports out and the bidirectional ports have the type in out in standard VHD L. The sizes of these signals are declared ( vlbit is the Viewlogic version of the bit, sirnilarly, one-dirnensional bit vectors are vlbit_ld(O to array size)) . The behavior part of the HOP autornaton is described as an architecture description in VHDL. In the case of a derived model (the exan1ple given below is a derived n1odel for a single phase clocking), we have a process with a wait staten1ent on the clock signal. The state encoding is first given. Each state is assigned a binary number and this number is mapped to a constant name. Other constants are described along with the state natnes. The data path state is then described. The data path variables in HOP directly translate to variables in VHDL. The variable cur_state which stands for current state and the variable nxLstate which stands for the next state are reserved variables. The data path state can include variables of various sizes such as single bit, one-dimensional, and two-dimensional arrays of bits ( the descriptions are currently in the View logic type formats). All the transitions and datapath state updates are described in terms of if- then - else and assignment statements. Outputs are a function of the states and therefore, they are asserted whenever the cur·_state variable has a particular encoded value. They have the format o <= v, where o is the name of the output port and vis the value driven on that port. A simplified example for an example module and its associated automaton diagrarn are given in Figure 2.6. 2. 7 Structural descriptions Various rnodules in a large system are connected together to provide a cornplete structural description. We assurne the following for structural descriptions. The connection between a rnem module and a checker module is shown in Figure 2. 7 |