| Publication Type |

technical report |

| School or College |

College of Engineering |

| Department |

Computing, School of |

| Creator |

Kudva, Prabhakar N. |

| Title |

A framework for hardware design analysis and synthesis using VHDL |

| Date |

1993-03 |

| Description |

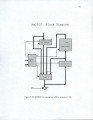

An approach for behavioral analysis and synthesis in a single framework is presented. The main advantage of specifying circuits at an abstract level is that they become amenable to formal analysis. A formalism HOP, which is an extended automaton model to describe behaviors of circuits is introduced. A set of static semantic checks called well-formedness checks is defined on the HOP automata to prevent common design errors in circuits synthesized from the behavior. An interconnection of behavioral descriptions, called a structural description, can be written and analyzed for well formedness. Algorithms for inferring an equivalent behavioral description from a given structural description have been developed. In order to avoid the creation of yet another HDL the HOP automaton has been embedded in a standard HDL, VHDL. Therefore, we have a formal semantic basis that is important in verification for the subset of VHDL denoted by HOP automata Standard VHDL based analysis and synthesis tools can be used. In addition, we have available a semantically correct way of inferring VHDL behavioral descriptions from VHDL structural descriptions. The inferred behavior in VHDL is useful in simulation, in simulation based verification and could be uscd in test generation tools. The above ideas have been implemented in the form of a C | | prototype, experiment have been performed with this prototype on a number of realistic designs, including the pipelined stack, pipelined cache memory system, AMD 2910 microprogram address sequencer and a switch level stack controller. The VHDL support comes from a commercial tool developed by Viewlogic Systems, Inc. |

| Type |

Text |

| Subject |

VHDL; computer hardware description language |

| Language |

eng |

| Bibliographic Citation |

Kudva, P. N. (1993). A framework for hardware design analysis and synthesis using VHDL. |

| Series |

University of Utah Computer Science Technical Report |

| Relation is Part of |

ARPANET |

| Format Medium |

application/pdf |

| Format Extent |

74,748,060 bytes |

| File Name |

Kudva-A_Framework_For.pdf |

| Conversion Specifications |

Original scanned with Kirtas 2400 and saved as 400 ppi uncompressed TIFF. PDF generated by Adobe Acrobat Pro X for CONTENTdm display |

| ARK |

ark:/87278/s6wh4r9d |

| Setname |

ir_computersa |

| ID |

99265 |

| Reference URL |

https://collections.lib.utah.edu/ark:/87278/s6wh4r9d |