# FORMAL VERIFICATION OF DEVICE DRIVERS IN EMBEDDED SYSTEMS

by

Jianjun Duan

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

School of Computing

The University of Utah

December 2013

Copyright © Jianjun Duan 2013

All Rights Reserved

# The University of Utah Graduate School

## STATEMENT OF DISSERTATION APPROVAL

| The dissertation | n of                  | •                | Jianjun Duan   |                                            |

|------------------|-----------------------|------------------|----------------|--------------------------------------------|

| has been appro   | ved by the following  | supervisory comm | ittee members: |                                            |

|                  | John Regehr           |                  | , Chair        | Jul 8 <sup>th</sup> , 2013  Date Approved  |

|                  | Matthew Flatt         |                  | , Member       | July 8th, 2013 Date Approved               |

| (                | Ganesh Gopalakrishr   | 1an              | , Member       | July 8 <sup>th</sup> , 2013  Date Approved |

|                  | Michael Norrish       |                  | , Member       | July 15 <sup>th</sup> , 2013 Date Approved |

|                  | Konrad Slind          |                  | , Member       | July 18 <sup>th</sup> , 2013 Date Approved |

| and by           |                       | Alan Davis       |                | , Chair/Dean of                            |

| the Departmen    | t/College/School of _ |                  | Computing      |                                            |

| and by David F   | R Kieda Dean of The   | Graduate School  |                |                                            |

#### ABSTRACT

Embedded systems are often deployed in a variety of mission-critical fields, such as car control systems, the artificial pace maker, and the Mars rover. There is usually significant monetary value or human safety associated with such systems. It is thus desirable to prove that they work as intended or at least do not behave in a harmful way.

There has been considerable effort to prove the correctness of embedded systems. However, most of this effort is based on the assumption that embedded systems do not have any peripheral devices and interrupt handling. This is too idealistic because embedded systems typically depend on some peripheral devices to provide their functionality, and in most cases these peripheral devices interact with the processor core through interrupts so that the system can support multiple devices in a real time fashion.

My research, which focuses on constrained embedded systems, provides a framework for verifying realistic device driver software at the machine code level. The research has two parts.

In the first part of my research, I created an abstract device model that can be plugged into an existing formal semantics for an instruction set architecture. Then I instantiated the abstract model with a model for the serial port for a real embedded processor, and plugged it into the ARM6 instruction set architecture (ISA) model from the University of Cambridge, and verified full correctness of a polling-based open source driver for the serial port.

In the second part, I expanded the abstract device model and the serial port model to support interrupts, modified the latest ARMv7 model from the University of Cambridge to be compatible with the abstract device model, and extended the Hoare logic from the University of Cambridge to support hardware interrupt handling. Using this extended tool chain, I verified full correctness of an interrupt-driven open source driver for the serial port.

To the best of my knowledge, this is the first full correctness verification of an interrupt-driven device driver. It is also the first time a device driver with inherent timing constraints has been fully verified. Besides the proof of full correctness for realistic serial port drivers, this research produced an abstract device model, a formal specification of the circular buffer at assembly level, a formal specification for the serial port, a formal ARM system-on-chip (SoC) model which can be extended by plugging in device models, and the inference rules to reason about interrupt-driven programs.

# CONTENTS

| ΑE  | BSTRACT                                                                                                                                                                                                                                                   | iii                                                 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                                                             | ix                                                  |

| LIS | ST OF TABLES                                                                                                                                                                                                                                              | xi                                                  |

| AC  | CKNOWLEDGMENTS                                                                                                                                                                                                                                            | xii                                                 |

| CH  | HAPTERS                                                                                                                                                                                                                                                   |                                                     |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                              | 1                                                   |

|     | 1.1 Thesis Statement 1.2 Challenges 1.2.1 Low-Level Nature 1.2.2 Parallelism and Concurrency 1.2.3 Timing Properties 1.2.4 Mechanical Proof 1.3 Background 1.3.1 Devices 1.3.2 Operational Semantics 1.3.3 Hoare Logic 1.3.4 HOL 1.4 Outline 1.5 Notation | 1<br>2<br>2<br>3<br>3<br>4<br>4<br>4<br>5<br>6<br>7 |

| 2.  | DEVICE MODEL                                                                                                                                                                                                                                              | 11                                                  |

|     | 2.1 Overview 2.1.1 System Model 2.1.2 Assertion Formula 2.2 Memory-Mapped I/O. 2.2.1 Abstract Device Model 2.2.2 Device Pool 2.3 Extended System Model 2.3.1 Reason about Multiple Devices                                                                | 11<br>12<br>13<br>13<br>14<br>14<br>15              |

| 3.  | CORRECTNESS PROOF FOR POLLING-BASED SERIAL PORTORIVER                                                                                                                                                                                                     | Γ<br>22                                             |

|     | 3.1 Serial Port                                                                                                                                                                                                                                           | 22<br>23<br>25<br>25<br>26                          |

|           | 3.4.2 Memory Safety and Control Flow Integrity |

|-----------|------------------------------------------------|

|           | 3.4.3 Correctness of the Serial Port Driver    |

|           | 3.4.4 Proof Method                             |

|           | 3.5 Summary                                    |

| 4.        | ARM SOC MODEL                                  |

|           | 4.1 Overview                                   |

|           | 4.1 Overview                                   |

|           | 4.3 Cambridge ARM Model                        |

|           | 4.3 Cambridge Arm Model                        |

|           | 4.3.1 ARM Core Model                           |

|           |                                                |

|           |                                                |

|           |                                                |

|           | 4.3.3.2 Hiding as Weakening                    |

|           | 4.3.4 Automation                               |

|           | 4.4 Extended ARM SoC Model                     |

|           | 4.4.1 Device Model with Interrupts             |

|           | 4.4.2 ARM SoC Model                            |

|           | 4.4.3 Atomic ARM Instruction Semantics         |

|           | 4.4.3.1 Atomic ARM Machine                     |

|           | 4.4.3.2 Atomic Instruction Semantics for SoC   |

|           | 4.4.4 Single-Step Hoare Logic for ARM SoC      |

|           | 4.4.4.1 Single-Step Hoare Logic                |

|           | 4.4.4.2 Single-Step Hoare Logic for ARM SoC    |

|           | 4.5 Hoare Logic for ARM SoC Model              |

|           | 4.5.1 Reintroduce Interrupts                   |

|           | 4.5.2 Inference Rules                          |

|           | 4.5.2.1 Integrate the Effect of the ISR        |

|           | 4.5.2.2 Introduce High-Level Assertions        |

|           | 4.5.3 Stack Model                              |

|           | 4.5.3.1 Automation of Stack Assertion          |

| <b>5.</b> | CORRECTNESS PROOF FOR THE SERIAL PORT ISR 69   |

|           | 5.1 Serial Port Model with Interrupts          |

|           | 5.1.1 Serial Port Interrupts Handling          |

|           | 5.2 Serial Port ISR                            |

|           | 5.3 Circular Buffer Model                      |

|           | 5.3.1 Circular Buffer                          |

|           | 5.3.2 Formalization of Circular Buffer         |

|           | 5.4 Correctness of the Serial Port ISR         |

|           | 5.4.1 High-Level View of the ISR Behavior      |

|           | 5.4.2 Timing Property                          |

|           | 5.4.3 tx Property                              |

|           | 5.4.4 rx Property                              |

|           | 5.4.4.1 String Abstraction                     |

|           | 5.4.4.2 rx Safety                              |

|           | 5.4.5 Hoare Triple for the Serial Port ISR     |

|           | 5.5 Proof                                      |

|    | 5.5.1 Proof Approach 5.5.1.1 High-Level Assertion Formula 5.5.1.2 Intermediate Assertion 5.5.2 Proof of the IRQ Loop 5.5.2.1 Switch Table 5.5.2.2 IRQ Loop | 82         |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6. | CORRECTNESS PROOF FOR INTERRUPT-DRIVEN SERIAL PORT DRIVER                                                                                                  | 100        |

|    | 6.1 Serial Port Driver                                                                                                                                     | 101        |

|    | 6.2 Assertion Formula for the ISR                                                                                                                          | 103        |

|    | 6.2.1 Interrupt Mode                                                                                                                                       | 103        |

|    | 6.2.2 THRE-Atomic Mode                                                                                                                                     | 104        |

|    | 6.3 Assertion Formula for uart0Putch                                                                                                                       | 104        |

|    | 6.3.1 Interrupt and Atomic Modes                                                                                                                           | 104        |

|    | 6.3.2 THRE-Atomic Mode                                                                                                                                     | 104        |

|    | 6.4 Resource Conflicts and Assertion Weakening                                                                                                             | 105        |

|    | 6.5 Effect of the ISR                                                                                                                                      | 107        |

|    | 6.5.1 Interrupt Mode                                                                                                                                       | 107        |

|    | 6.5.2 THRE-Atomic Mode                                                                                                                                     | 107        |

|    | 6.6 Correctness of uart0Putch                                                                                                                              | 107        |

|    | 6.7 Proof Methods                                                                                                                                          | 108        |

|    | 6.7.1 Assertion Propagation                                                                                                                                | 108        |

|    | 6.7.2 Inlining                                                                                                                                             | 109        |

|    | 6.7.3 Conditional Execution                                                                                                                                | 109        |

|    | 6.7.4 Weakening and Live Variables                                                                                                                         | 109        |

|    | 6.7.5 Automation                                                                                                                                           | 110<br>111 |

|    | 6.8 Benign Racing and Nonmonotonic Branch                                                                                                                  | 111        |

| 7. | CONCLUSION                                                                                                                                                 | 127        |

| 8. | FUTURE WORK                                                                                                                                                | 128        |

|    | 8.1 Multiple Devices                                                                                                                                       | 128        |

|    | 8.2 Initialization Code                                                                                                                                    |            |

| 9. | RELATED WORK                                                                                                                                               | 131        |

|    | 9.1 Formal Semantics of ISAs                                                                                                                               | 131        |

|    | 9.2 Program Logic for Machine Languages                                                                                                                    | 132        |

|    | 9.3 Taming Concurrency in Interrupt-Driven Systems                                                                                                         | 134        |

|    | 9.4 Formal Methods on Interrupt-Driven Embedded Systems                                                                                                    | 135        |

|    | 9.5 Verification of Device Drivers                                                                                                                         | 135        |

|    | 9.5.1 Correctness of Device Drivers                                                                                                                        | 135        |

|    | 9.5.2 Property Checking for Device Drivers                                                                                                                 | 136        |

|    | 9.5.3 Device Driver Synthesis                                                                                                                              | 137        |

| DE | FFRENCES                                                                                                                                                   | 122        |

# LIST OF FIGURES

| 1.1  | System with devices                                                                                                              | 9  |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The flow of technical work                                                                                                       | 10 |

| 2.1  | Combination of devices                                                                                                           | 17 |

| 2.2  | Model for system with devices                                                                                                    | 18 |

| 2.3  | Parallel nature of next                                                                                                          | 19 |

| 2.4  | sys_pred definition used to reason about embedded systems with multiple devices                                                  | 20 |

| 2.5  | Plugging in a new device does not break the existing system                                                                      | 21 |

| 3.1  | Formula used to assert the serial port state                                                                                     | 32 |

| 3.2  | ARM assembly code for putch, getch and getchw                                                                                    | 33 |

| 3.3  | Safety property for the transmitting function in the serial port model .                                                         | 34 |

| 3.4  | Safety property for the receiving function in the serial port model                                                              | 35 |

| 3.5  | Correctness theorem for putch                                                                                                    | 36 |

| 3.6  | Correctness theorem for getch                                                                                                    | 37 |

| 3.7  | Correctness theorem for getchW                                                                                                   | 38 |

| 4.1  | Semantics of instruction $STRB\ r2,\ [r3]\ \mathrm{in}\ \mathrm{the}\ \mathrm{Cambridge}\ \mathrm{ARM}\ \mathrm{model}\ .$       | 55 |

| 4.2  | Hoare triple for instruction STRB r2, [r3] in the Cambridge ARM model                                                            | 56 |

| 4.3  | Abstract model for devices with interrupts                                                                                       | 57 |

| 4.4  | Memory read primitive for the ARM SoC model                                                                                      | 58 |

| 4.5  | Semantics for ARM_ENTER_IRQ                                                                                                      | 59 |

| 4.6  | Memory access scenario for instruction STRB r2, [r3] in the ARM SoC model                                                        | 60 |

| 4.7  | Device access scenario for instruction STRB r2, [r3] in the ARM SoC model                                                        | 61 |

| 4.8  | Semantics of instruction STRB r2, [r3] in the case of memory access in the single-step Hoare logic                               | 62 |

| 4.9  | Semantics of instruction STRB r2, [r3] in the case of device access in the single-step Hoare logic                               | 63 |

| 1.10 | One can derive the single-step semantics without interrupts pending from the single-step atomic semantics for an ARM instruction | 64 |

| 4.11 | One can derive the single-step semantics with interrupts pending from<br>the single-step atomic semantics for an ARM instruction                                                                                                                                                             | 65  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.12 | Inference rule for integrating the invariant effect of an ISR                                                                                                                                                                                                                                | 66  |

| 4.13 | Inference rule for integrating the effect of an ISR                                                                                                                                                                                                                                          | 67  |

| 4.14 | Inference rule for introduing high-level assertion formula                                                                                                                                                                                                                                   | 68  |

| 5.1  | Handling of different interrupt sources in the serial port model                                                                                                                                                                                                                             | 88  |

| 5.2  | ARM assembly code for the serial port ISR                                                                                                                                                                                                                                                    | 89  |

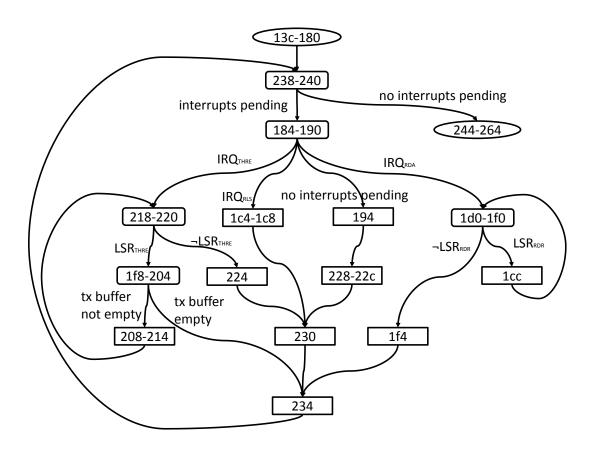

| 5.3  | CFG of the ISR. Oval shape indicates the entry or exit block. Round rectangle shape indicates branches.                                                                                                                                                                                      | 90  |

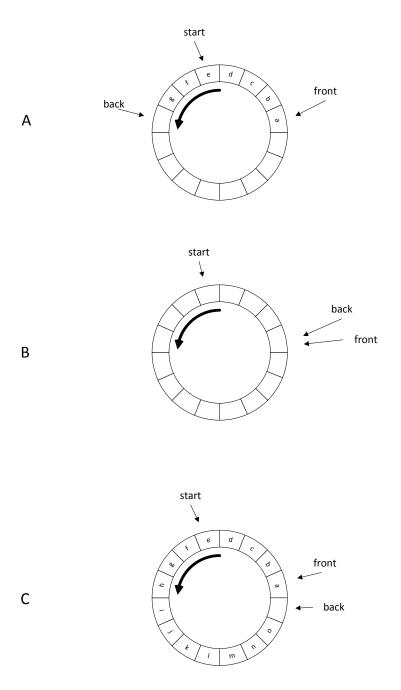

| 5.4  | Circular buffer. The figure shows a circular buffer with size 16 at different stages of operation. In A, a list of [a;b;c;d;e;f;g] is stored in the buffer. In B, the buffer is empty. In C, the buffer is full, yet 1 slot is not used. The arced arrow indicates the growth of array index | 91  |

| 5.5  | circBuf definition                                                                                                                                                                                                                                                                           | 92  |

| 5.6  | Circular buffer properties                                                                                                                                                                                                                                                                   | 93  |

| 5.7  | aU definition                                                                                                                                                                                                                                                                                | 94  |

| 5.8  | Theorems showing accumulation of the minimum cushion time                                                                                                                                                                                                                                    | 95  |

| 5.9  | Monotonicity of the cushion time                                                                                                                                                                                                                                                             | 96  |

| 5.10 | Definitions of sample and ishifted                                                                                                                                                                                                                                                           | 97  |

| 5.11 | Definition of lantency                                                                                                                                                                                                                                                                       | 99  |

| 6.1  | ARM assembly code for $uart0$ Putch                                                                                                                                                                                                                                                          | 113 |

| 6.2  | ARM assembly code for $disableIRQ$ and $restoreIRQ$                                                                                                                                                                                                                                          | 114 |

| 6.3  | Formula used to assert the ISR in interrupt mode                                                                                                                                                                                                                                             | 115 |

| 6.4  | Formula used to assert the ISR in THRE-atomic mode                                                                                                                                                                                                                                           | 116 |

| 6.5  | Formula used to assert $uart0Putch$ in interrupt mode and atomic mode.                                                                                                                                                                                                                       | 117 |

| 6.6  | Formula used to assert $uart0Putch$ in THRE-atomic mode                                                                                                                                                                                                                                      | 118 |

| 6.7  | Abstraction of the assertion formula for the serial port ISR in different modes                                                                                                                                                                                                              | 121 |

| 6.8  | Abstraction of the assertion formula for $u0Putch$ in different modes $\ldots$                                                                                                                                                                                                               | 122 |

| 6.9  | Hoare triple for the ISR in interrupt mode                                                                                                                                                                                                                                                   | 123 |

| 6.10 | Hoare triple for the ISR in THRE-atomic mode $\hdots$                                                                                                                                                                                                                                        | 124 |

| 6.11 | Hoare triple for the working branch of uart0Putch                                                                                                                                                                                                                                            | 125 |

# LIST OF TABLES

| 3.1 | Serial port model coverage. R indicates read-only registers; W indicates write-only. RW indicates no restriction on access. The first four columns are from data in the LPC2129 manual        | 31  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Serial port model with interrupts. R indicates read-only registers; W indicates write-only. RW indicates no restriction on access. The first four columns are from data in the LPC2129 manual | 86  |

| 5.2 | Serial port model interrupts coverage. The first two columns are adapted from the LPC2129 manual                                                                                              | 87  |

| 5.3 | Placeholders used in the Hoare triple for the ISR                                                                                                                                             | 98  |

| 6.1 | High-level view of low-level system resources                                                                                                                                                 | 119 |

| 6.2 | Resource conflicts between $uart0Putch$ and the ISR                                                                                                                                           | 120 |

| 6.3 | Placeholders used in the Hoare triple for uart0Putch                                                                                                                                          | 126 |

#### ACKNOWLEDGMENTS

First of all, I want to thank my advisor, Professor John Regehr. He guided me into the area of applying formal methods on embedded systems, and helped me to develop the dissertation topic. Without his guidance and support, this dissertation would not be possible.

I am also very grateful to my former advisor, Dr. Konrad Slind. He taught me a lot about the formal methods, especially the theorem prover HOL, which is the major tool I used in my dissertation work.

I also thank my committee members: Professor Ganesh Gopalakrishnan, Professor Matthew Flatt, and Dr. Michael Norrish. I learned a lot about formal methods, functional programming and HOL from them. Discussion with them helps me expand the horizon of my research.

I also had inspiring discussions about the ARM model inside HOL and research ideas with Dr. Anthony Fox and Dr. Magnus Myreen from the University of Cambridge. I thank them for their contribution to my research.

Fellow students and friends, Xiaofang Chen, Yang Chen, Guodong Li, Peng Li, Xuejun Yang, Yu Yang and Lu Zhao, also helped me a lot in these years both in academics and daily life. I thank them for their help.

I also thank Karen Feinauer and Ann Carlstrom. They handled all my paperwork and helped me a lot on technical problems outside my research. It was great to have them in the front office in these years.

#### CHAPTER 1

#### INTRODUCTION

Embedded systems are often deployed in fields where there is significant risk of human safety or property. Thus it is desirable to guarantee that they work as intended or at least do not behave harmfully. Some examples are car control systems, artificial pace makers, and the Mars rover.

Generally speaking, formal verification can be used to provide rigorous guarantees. However, the vast majority of verification work on embedded systems ignores devices and device drivers. This is problematic because an embedded system is tailored around a set of devices to perform a dedicated task.

The tailoring is done at both hardware and software levels. At the hardware level, only necessary peripheral devices are built into the system without much flexibility to expand. Some common peripheral devices include the serial port, analog-digital converter (ADC), and timer. At the software level, the system can be viewed as little more than necessary device drivers and a simple control loop. Device drivers are often specialized.

In this dissertation I will address this deficiency in current research of formal verification of embedded systems using a theorem prover. My goal is to prove the correctness of realistic drivers on embedded systems with peripheral devices working in interrupt mode. I will develop a framework. The effectiveness of the framework will be demonstrated by some realistic examples.

#### 1.1 Thesis Statement

Formal proof about functional correctness of realistic device drivers on embedded systems with memory mapped devices working in interrupt mode can be done using theorem proving tools.

Previous work in low-level machine models and machine-level program logic using theorem proving tools provides a good foundation. My idea is to expand existing machine models and program logic to support hardware devices and interrupts.

First, I introduce a device model which can be combined with an instruction set architecture (ISA) model to verify device drivers. Then it is extended to support interrupts. Finally, I add program logic support for reasoning software taking advantage of interrupts.

It will be implemented in HOL [39] on top of the ARM ISA model [33, 60]. The method is applied to verify functional correctness of an open source driver for the serial port, which is used to receive and transmit data.

#### 1.2 Challenges

There are substantial challenges for this dissertation work. To verify an interrupt-driven system, it is better to work at the assembly level. This, however, exposes all the low-level details. Parallelism associated with interrupts is complicated because of side effects in device register access. Realistic drivers and ISRs often have inherent timing constraints. Rigorous proof often comes at the cost of laborious effort.

#### 1.2.1 Low-Level Nature

The programmability of a system at register level allows a wide range of flexibility in software, which hinders the portability of some generic methodologies. One example is the variety of interrupt handling schemes that can be implemented on the same hardware platform. Another one is the optimizations of a program at assembly level.

Access of device registers has side effects. One has to have an accurate understanding of them at the register level to reason about device drivers. Such side effects make the concurrency between interrupt handlers and the main program more complicated than the one between threads.

#### 1.2.2 Parallelism and Concurrency

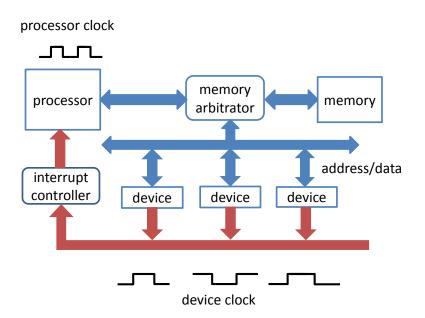

As shown in Figure 1.1, a device runs in parallel with the processor core. Its state changes by itself (with possible input from the environment) or as the side effect of

<sup>&</sup>lt;sup>1</sup>I use assembly and machine language interchangeably in verification context.

commands from the processor core. The interaction between them can be two-way.

The processor core sends a command to a device by reading from or writing to some particular memory address which is mapped to a register on the device. The devices can force the processor core to execute some code, called interrupt handlers, by interrupting its normal execution of the main program through interrupts, which are triggered by some hardware events. The device driver will package such interactions, and provide a high-level application program interface (API).

Now, even for a system with a single thread, a device driver (execution of the processor core) is a parallel entity to the devices that it manages, and the interrupt handlers run concurrently with the main program. This makes testing not a convincing approach to provide trustworthy guarantees about the functionality and safety of the system, because complete coverage is not possible.

#### 1.2.3 Timing Properties

Often interesting properties of an embedded system are associated with time. For example, it is often assumed that interrupts are handled in a timely manner. Only then can the function of an interrupt service routine (ISR)<sup>2</sup> be guaranteed. Another example is that there are always restrictions on the speed of devices, such as data throughput and the maximum frequency of interrupt requests.

In temporal logic [19, 24, 49, 73], time is modeled as one time line or a tree structure with multiple possible future branches. Here, the notion of time describes the rate at which an event can occur. Formalization of embedded systems needs to account for it.

#### 1.2.4 Mechanical Proof

The ideal guarantee I am after is a mathematical proof. However, given the challenges, it is not plausible by a paper-and-pencil proof as done in an algorithm class. A mechanical proof is necessary.

To verify nontrivial properties of a piece of realistic software on a realistic embedded system, one needs to formalize the system with plenty of low-level details, reason about concurrency abstractly at a high level, and automate as much as possible.

<sup>&</sup>lt;sup>2</sup>I use ISR and interrupt handlers interchangeably in this dissertation.

A theorem prover is necessary for achieving these tasks, especially to ensure the soundness of proofs.

#### 1.3 Background

This dissertation work involves formalizing an abstract device model which can used in verification of different devices and their drivers, the operational semantics of ARM assembly language on a machine with devices, program logic support for high-level proof, and formalization using HOL theorem prover. Here is a brief overview of these subjects.

#### 1.3.1 Devices

Formal semantics of a language are usually defined on an abstract machine. In most cases, the state of the machine consists of memory and registers. However, in practice, often extensions are made to languages so that the semantics are defined on machines whose states include more than memory and registers.

One such extension is memory-mapped I/O. It introduces side effects to memory access when the address is mapped to a device register. This means that to prove properties about a program which accesses memory-mapped I/O, formal semantics need be developed for the language on an abstract machine with devices. Side effects need be addressed.

Such formal semantics should be built for assembly languages. Doing so means compilers are not in the Trusted Computing Base (TCB) any more. There is plenty of evidence suggesting that compilers cannot be trusted [101]. Assembly language is still used in mission critical embedded systems for reasons such as performance and resource constraints. Also, for device operations as well as interrupt handling, high-level languages do not provide fine enough granularity in terms of temporal resolution.

#### 1.3.2 Operational Semantics

On the other hand, we can just use an operational semantics of a language to prove the properties of a program, as pointed out by Moore [57]. In operational semantics, the meaning of a program is seen as a sequence of transition on the state which the program lives on. Such transition is described by a step function:  $s_t = \text{step }(s_{t-1})$ . When the operational semantics of a programming language are formalized in an interactive theorem prover, one can try to prove almost any goal conceivable about a program. In most cases however, it is not efficient, since lots of work will be repeated in a proof.

To improve the performance, a Hoare logic [31, 42] can be built on top of the formal operational semantics. Program logic provides high-level inference rules. In tricky situations when high-level inference rules fail, one can always attempt the proof at the level of operation semantics.

#### 1.3.3 Hoare Logic

When proving some property about a program, the program must be treated as a mathematical object. Hoare logic provides a way to do so. A program is built from statements following grammar rules. In Hoare logic, an axiom is used to describe the precondition and postcondition of a statement in the form of  $\{P\}$  C  $\{Q\}$ . This is a Hoare triple. Here, C is the statement, P is the precondition assertion, and Q is the postcondition assertion. For each grammar rule, corresponding inference rules are given.

The property of a program is also specified in terms of a Hoare triple. There are two ways to prove the Hoare triple for a program. One is the top-down approach, in which the Hoare triple for a program is broken down into subgoals about the statements of the program using inference rules. This process is called verification condition generation. Another is the bottom-up approach, in which inference rules are used to compose the axioms of individual statements together to form the final theorem about the program.

Using Hoare logic to prove properties about a realistic program in a realistic programming language is not easy. One problem is efficiency. Burstall [15] realized that for some data structures like list, the naive way of specifying memory properties would not scale. Separation logic [80] is developed to address such issues. In separation logic reasoning is done locally using the frame rule:  $\{P\}$   $C\{Q\} \Rightarrow \{P*P'\}$   $C\{Q*Q'\}$ . Here, \* is separation conjunction, x\*y means x and y hold on two separated sets of resources. Further down the line concurrent separation logic [13] is developed to

reason about concurrency.

Another problem is how to support language features in terms of inference rules. Most commonly used languages present their own unique challenges. For example, a Hoare logic for C needs to address the flexible memory model, like in L4 verification project [95]. For assembly languages, rather complex control flow has to be supported [93].

#### 1.3.4 HOL

HOL is an interactive theorem prover for higher order logic. It is built using the LCF approach [40], which gives it soundness guarantee on the theorems proved using it. A lot of work has been done to formalize the ARM ISA in HOL by Fox et al. [33, 37] at the University of Cambridge. It is low level and faithful to the ARM standard as demonstrated by the verification of the ARM6 microarchitecture.

The Hoare logic [60] built on top of it supports separation logic style reasoning. For example, ARM instruction STRB r2, [r3] stores the least significant byte in register r2 at the memory location pointed to by the pointer in register r3. The Hoare triple for it is:

```

\begin{split} & (\mathsf{aPC}\ p*\mathsf{aR}\ 3\ a*\mathsf{aR}\ 2\ b*\mathsf{aBYTE\_MEMORY}\ df\ f*\mathsf{cond}(a\in df)) \\ & \{\ (p,0\mathsf{xE5C32000})\ \} \\ & (\mathsf{aPC}\ (p\ +4)*\mathsf{aR}\ 3\ a*\mathsf{aR}\ 2\ b*\mathsf{aBYTE\_MEMORY}\ df\ ((a\mapsto b\!\uparrow_{32}^8)\ f)). \end{split}

```

It states this at the machine level: If the program counter holds value p (aPC p), register 2 holds value b (aR 2 b), register 3 holds value a (aR 3 a), and instruction 0xE5C32000 (the binary encoding of STRB r2, [r3]) resides at the address p of the memory (p, 0xE5C32000), and that a is a valid memory address (cond ( $a \in df$ )), then after the execution of the processor the program counter will increase by 4, and the memory (aBYTE\_MEMORY df) will be updated such that the cell at address a now holds value b.  $b \uparrow_{32}^{8}$  is the least significant byte of b. for an ARM assembly program, if theorems like this for all its instructions are available, they can be composed to form the specification of the program. My work is built upon this ARM ISA model. I extended the ARM ISA model to support device access, and extended the Hoare

logic to support interrupt handling.

#### 1.4 Outline

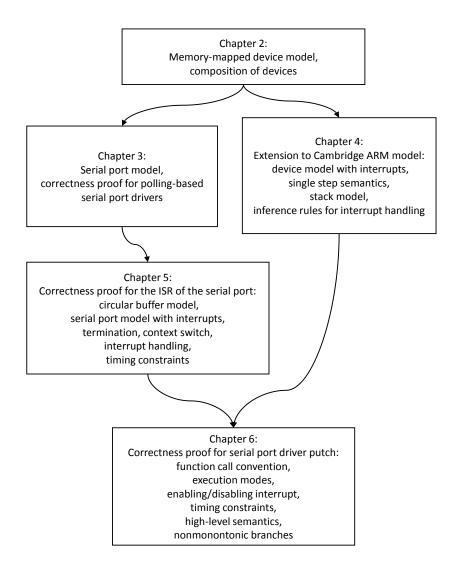

I present a progressive work in two parts in this dissertation. The flow of the technical work including ideas and theorems is shown in Figure 1.2. An arrow from A to B indicates the idea or theorems in A is expanded or applied in B. Chapters 2 and 3 form the first part, which is about verifying a polling based device driver. An abstract device model for using with an ISA model is presented in Chapter 2, which forms the foundation of my work. In Chapter 3, I present the serial port model without supporting interrupts, and prove the functional correctness of a polling-based serial port driver.

Chapters 4, 5 and 6 form the second part. In this part I present my approach to verify interrupt-driven device drivers and demonstrate it by verifying an interrupt-driven serial port driver. In Chapter 4, I overview ARM related research work done at the University of Cambridge, and develop the semantics for the ARM SoC model, as well as the support in program logic. The correctness proof for the ISR of the serial port as a standalone program is presented in Chapter 5. In Chapter 6, I present the correctness proof of an interrupt-driven serial port driver.

I summarize the work in Chapter 7. Future work is proposed in Chapter 8, and related work is discussed in Chapter 9.

#### 1.5 Notation

Here, I introduce some of the notations used in this dissertation.

- 1. Almost all the constant numbers are actually words of fixed width, except the parameters I use to count time elapse.

- 2. I used different fonts to differentiate a variable and a function or keyword. defined is a keyword. function is a function name. *var* is a variable.

- 3. Every variable is a free variable at the top level<sup>3</sup> unless it is explicitly qualified.

- 4. Every theorem starts with. Small theorems are presented in equations, while large ones are in figures.

$<sup>^3</sup>$ It is equivalent to a universally qualified variable in HOL as far as the meaning of theorems is concerned.

- 5. Underlined terms such as <u>placeholder</u> are not ordinary variables. They are placeholders for constant and complex formulas, and used to make formula and theorems more readable.

- 6. For some processor registers and device registers, it is common to refer to the individual bits of them. I use the capitalized bit name as subscript to denote a bit in a register. For example, PSR<sub>I</sub> means the interrupt mask bit in a processor status register (PSR), IER<sub>RLS</sub> denotes the receiving line status (RLS) bit in the Interrupt Enable Register (IER) of the serial port.

- 7. Definition is indicated by  $\triangleq$ .

Memory is modeled as a map from 32-bit word to byte (8-bit word). Little-endianness is followed. Following symbols are used to denote some operations on memory and words:

- 1.  $f \nearrow_{\mathbf{m}}^{\mathbf{n}}$  addr means reading m bytes from addresses starting from addr first, then concatenating them into a  $m \times 8$ -bit word, and finally converting it to a n-bit word by zero-extending it or discarding the extra more significant bits.

- 2.  $\overleftarrow{addr}^n$  returns the set  $\{addr, addr+1, \cdots, addr+n-1\}$ . It is used to return the set of addresses starting from the given address in a multibyte memory access.

- 3.  $x \uparrow_{\mathbf{m}}^{\mathbf{n}}$  converts a *m*-bit word *x* to a *n*-bit word by zero-extending it or discarding the extra more significant bits.

- 4.  $+_x$  denotes modular word addition with regard to x.

- 5. Subscript + in comparison operators such as  $\leq_+$  means unsigned operation.

Figure 1.1: System with devices

Figure 1.2: The flow of technical work

#### CHAPTER 2

#### DEVICE MODEL

In this chapter I present an abstract device model which is to be used with an ISA model. The target ISA model is the ARMv4 model [33] by Fox.

#### 2.1 Overview

Fox's ARM model includes banked registers including special purpose registers, exceptions, coprocessors, and a data bus. A system model with no coprocessors and no interrupt handling is built by extending the core model with memory through the data bus. Its next-state operation is at the instruction level; it takes a system state as the input and returns the next state as the result of current instruction execution. There are tools to automatically prove theorems about the semantics of individual concrete ARMv4 instructions.

#### 2.1.1 System Model

An embedded system is modeled using this record:

$$<$$

| next : state  $\rightarrow$  state; is\_undefined : state  $\rightarrow$  bool | >. (2.1)

→ is used to represent function types. state is the type of the state of the system. next is used to encode the transition of the system, which includes fetching and parsing an instruction, fetching data, computing, updating registers, memory, and the state of devices. The is\_undefined predicate tests if a state is erroneous. The system enters an erroneous state when the processor core encounters an exceptional condition<sup>1</sup>, when the processor core accesses the memory addresses which are mapped to some device that is not present in the system, or when a device-specific error is encountered, i.e.,

<sup>&</sup>lt;sup>1</sup>I do not consider the handling of interrupts or processor exceptions here.

reading a device register that is in an indeterminate state or writing to a read-only device register.

It is required that:

is\_undefined

$$s \Rightarrow$$

is\_undefined (next  $s$ ).

That is, an erroneous state is sticky and we are not concerned with the system's subsequent behavior. One of my goals will be to prove that device drivers cannot put the system into an erroneous state.

A function step describes the effect of consecutive application of next:

step

$$n \ s \triangleq \text{if } n = 0 \text{ then } s \text{ else next (step } (n-1) \ s).$$

For step to describe a running system, memory values including both instructions and data must be part of the system state. But that is not enough. For example, the processor can use values obtained by a sensor device from the environment to change the memory content. For cases like this, it is required that the state of the related device contain input streams, which need to contain the information from the future.

#### 2.1.2 Assertion Formula

I use the following construct to assert the properties of a state for the system:

$$\begin{split} & \mathsf{sys\_pred}\ P\ I\ Q \triangleq \\ & \forall s.\ P\ s \land \neg \mathsf{is\_undefined}\ s \Rightarrow \\ & \exists\ t.\ Q\ (\mathsf{step}\ t\ s) \land \\ & \forall\ n.\ n \leq t \Rightarrow I\ (s,\mathsf{step}\ n\ s) \land \neg \mathsf{sys\_undefined}\ (\mathsf{step}\ n\ s\ ). \end{split} \tag{2.2}$$

This is a shallow embedding of Hoare logic with P, I, and Q as the predicates of precondition, global invariant, and postcondition with type state  $\rightarrow$  bool. Note that this is about complete correctness.

To use this construct to describe the properties of a program, the program must be specified in terms of the current program counter and instruction memory. The value of the program counter and the instruction memory should be specified as part of P. I represent the program as a set of pairs of an instruction and its address. I use

code p s to indicate a program p is part of the memory in a system state s.

In most cases, the part of memory which holds the program should be left unchanged at every moment. That should be part of I.

To prove a claim in the form of Equation 2.2, an instance of t needs to be found first. Then induction on n is used. I use this method to prove the full correctness of a serial port driver working in the polling mode.

### 2.2 Memory-Mapped I/O

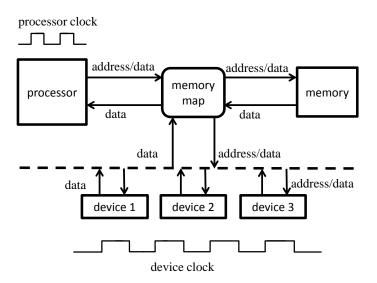

Embedded systems mostly have peripheral devices built in. The mechanism is memory-mapped I/O. Here, I introduce an abstract device model for memory-mapped I/O. It is intended to work with an ISA model.

#### 2.2.1 Abstract Device Model

A peripheral device runs in parallel with the processor core. Its state can change with or without interacting with the core or with the external world. The core interacts with devices using memory-mapped I/O: a collection of dedicated registers that are mapped into the processor's address space. From the perspective of the core, these registers are accessed like memory locations, though of course device registers do not in general contain the last value written to them, and both reads and writes may have side effects.

Based on this observation, I design an abstract type to represent a generic memorymapped peripheral device:

```

<|mapped : addr \rightarrow bool;

mapped_read : addr \rightarrow \tau \rightarrow word * bool * \tau;

mapped_write : addr \rightarrow data \rightarrow \tau \rightarrow bool * \tau;

transit : \tau \rightarrow \tau; wellform : \tau \rightarrow bool | >. (2.3)

```

Here, addr and word are types for memory addresses and data.  $\tau$  is the type for the state of the device, which varies depending on the individual device. \* is used to construct a tuple. mapped describes if an address is mapped to this device. mapped\_read and mapped\_write describe the effect of read and write commands from the processor core. Possible side effect on the device states is captured by  $\tau$  in

input and return types. The flag with bool type indicates if an error occurs during the memory-mapped access of the device registers. transit describes the autonomous transition of the device itself without the command from the processor core. wellform tells if a state of the device is wellformed. I use  $\tau$  dev to refer to the type of the device as in Equation 2.3.

A concrete device such as a serial port is modeled as an instance of this abstract model.  $\tau$  is instantiated with a concrete type, and all the members are assigned functions which model the concrete device.

#### 2.2.2 Device Pool

Device models can be repeatedly combined as long as they fail to share mapped registers (real devices have this property, generally). The operation is defined in Figure 2.1. Here, FST and SND return the first and second member of a pair type, respectively. With comb\_dev I can construct and reason about an embedded system with multiple devices modularly.

#### 2.3 Extended System Model

An embedded SoC is a processor core plus a collection of peripherals. I start with a processor core that is extended with a null device whose mapped function returns false for all addresses. I can then build a realistic SoC as shown in Figure 2.2 by adding more devices on top of this bare one, using the operations in Figure 2.1.

The state of a system with devices is modeled using this record:

```

<|regs : reg \rightarrow word; memory : addr \rightarrow word; dev_state : \tau; undefined : bool|>.

```

ext\_state extends the system state s with a device state ps:

```

ext_state ps \ s \triangleq < | \operatorname{regs} := s.\operatorname{regs}; \operatorname{memory} := s.\operatorname{memory}; \operatorname{dev\_state} := (ps, s.\operatorname{dev\_state}); \operatorname{undefined} := s.\operatorname{undefined} | >,

```

while base\_state undoes it:

```

base_state s \triangleq < | \operatorname{regs} := s.\operatorname{regs}; \operatorname{psrs} := s.\operatorname{psrs}; \operatorname{memory} := s.\operatorname{memory}; \operatorname{dev\_state} := \operatorname{SND} s.\operatorname{dev\_state}; \operatorname{undefined} := s.\operatorname{undefined} | >.

```

Here, reg is the type of a register, regs represents the register store, which includes the data registers and special purpose registers such the program counter and processor status registers. I use  $r_0$  to indicate register 0,  $r_{14}$  to indicate register 14, etc. pc is used to indicate the program counter. They are all of reg type. memory represents the memory. dev\_state represents the state of the devices. The system is in an erroneous state when undefined is set.

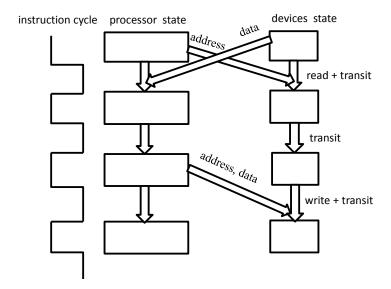

Given a state s, is\_undefined  $s \triangleq s$ .undefined. next in Equation 2.1 should implement the execution of the processor core and transit for the device in parallel, as shown in Figure 2.3. They are independent of each other except when the instruction is a command to the device. In this scenario, the processor core commands the device to run mapped\_read or mapped\_write and reads data from or writes data to the specific device register. It may set undefined based on the results of these operations. At the same time, when running mapped\_read or mapped\_write the device updates its state. The device finally updates its state again with transit.

#### 2.3.1 Reason about Multiple Devices

To support the modularity when reasoning about systems with multiple devices, I refine the definition in Equation 2.1 and use

$$<$$

| next :  $au$  dev  $\rightarrow$  state  $\rightarrow$  state; is\_undefined : state  $\rightarrow$  bool |  $>$

to model an embedded system. Similarly, the new step is

step

$$p$$

$n$   $s \triangleq \text{if } n = 0 \text{ then } s \text{ else next } p \text{ (step } p \text{ } (n-1) \text{ } s).$

The new sys\_pred is defined in Figure 2.4.

The theorem in Figure 2.5 establishes that adding a new device does not break a system that was previously working. If a system does not run into an erroneous state in t steps running a program, it will not run into an erroneous state in t steps running the same program with device  $p_2$  plugged in.

It is obvious that the program does not access the addresses mapped to  $p_2$  in these t steps. Otherwise it would have run into an erroneous state. So there is no chance for  $p_2$  to introduce errors to the program in these t steps. In other words, s and ps

are independent of each other in these t steps.

Also, if we can verify a property of a program in a system with only some set of peripherals, the property still holds when more devices are added:

$$\vdash (\forall \, a. \, \neg (p_1.\mathsf{mapped} \, \, a \wedge p_2.\mathsf{mapped} \, \, a)) \Rightarrow$$

$$\mathsf{sys\_pred} \, \, p_1 \, P \, I \, Q \Rightarrow$$

$$\mathsf{sys\_pred} \, \, (\mathsf{comb\_dev} \, p_2 \, p_1) \, (P \, \mathsf{o} \, \, \mathsf{base\_state})$$

$$(I \, \mathsf{o} \, (\lambda \, (x,y).(\mathsf{base\_state} \, x, \mathsf{base\_state} \, y))) \, (Q \, \mathsf{o} \, \, \mathsf{base\_state}). \tag{2.4}$$

For any system with device  $p_1$ , if  $sys_predp_1P I Q$  holds on it, then it holds for the system with one more device  $p_2$  added, considering only the state components before the plugging in of device  $p_2$ .

sys\_pred  $p_1$  P I Q actually specifies a sequence of transitions of the system. Similar to the theorem in Equation 2.4, in the new system, those components of the system state before the plugging in of device  $p_2$  and state of device  $p_2$  are independent of each other in the sequence. So the sequence specified by sys\_pred  $p_1$  P I Q is still the same.

```

comb_dev p_1 p_2 \triangleq

< | mapped := \lambda \ a. \ p_1.mapped \ a \lor p_2.mapped \ a;

mapped_read :=

\lambda \ a \ s. if p_1.mapped a

then let read_1 = p_1.mapped_read a (FST s) in

(FST read_1, (FST o SND) read_1, (SND o SND) read_1, SND s)

else if p_2.mapped a

then let read_2 = p_2.mapped_read a (SND s) in

(FST read_2, (FST o SND) read_2, FST s, (SND o SND) read_2)

else (ARB, T, s);

mapped_write :=

\lambda \ a \ d \ s. if p_1.mapped a

then let write_1 = p_1.mapped_write a \ d (FST s) in

(FST write_1, SND write_1, SND s)

else if p_2.mapped a

then let write_2 = p_2.mapped_write a \ d \ (SND \ s) in

(FST write_2, FST s, SND write_2)

else (\mathsf{T}, s);

transit := \lambda s. let np_1 = p_1.transit (FST s) and np_2 = p_2.transit (SND s) in

(np_1, np_2);

wellform := \lambda s. p_1.wellform (FST s) \wedge p_2.wellform (SND s) |>

```

Figure 2.1: Combination of devices

Figure 2.2: Model for system with devices

Figure 2.3: Parallel nature of next

```

\begin{split} & \mathsf{sys\_pred} \ p \ P \ I \ Q \triangleq \\ & \forall \, s. \ P \ s \land \neg \mathsf{is\_undefined} \ s \Rightarrow \\ & \exists \, t. \ Q \ (\mathsf{step} \ p \ t \ s) \land \\ & \forall \, n. \ n \leq t \Rightarrow I \ (s, \mathsf{step} \ p \ n \ s) \land \neg \mathsf{is\_undefined} \ (\mathsf{step} \ p \ n \ s \ ) \end{split}

```

Figure 2.4: sys\_pred definition used to reason about embedded systems with multiple devices

```

\begin{split} \vdash (\forall \ a. \ \neg (p_1.\mathsf{mapped} \ a \land p_2.\mathsf{mapped} \ a)) \Rightarrow \\ \forall \ t. \ \neg \mathsf{is\_undefined} \ (\mathsf{step} \ p_1 \ t \ s) \Rightarrow \\ \neg \mathsf{is\_undefined} \ (\mathsf{step} \ (\mathsf{comb\_dev} \ p_2 \ p_1) \ t \ (\mathsf{ext\_state} \ ps \ s)) \end{split}

```

$\textbf{Figure 2.5} : \ \textbf{Plugging in a new device does not break the existing system}$

#### CHAPTER 3

# CORRECTNESS PROOF FOR POLLING-BASED SERIAL PORT DRIVER

In this chapter I demonstrate the approach introduced in Chapter 2 by presenting the correctness proof for a polling-based serial port driver. First, I briefly introduce the communication functions of the serial port. Next, I develop the formal model for the serial port. Next, the assertion formula used to describe the high-level behavior of the serial port is introduced. Then I present the correctness theorems for the polling-based serial port driver, as well as the proof techniques. At the end I summarize the first part of my work, which will be used in the second part.

#### 3.1 Serial Port

A serial port, also known as universal asynchronous receiver/transmitter (UART), is a serial communication device. It is very common in computer systems, especially embedded systems.

The device has two basic communication functions: receiving and transmitting. It uses a clock divider to control the rate of receiving and transmitting, which is called baud rate. For the receiving function, when incoming data is received, it is assembled and placed in a hardware receive buffer register (RBR) if there is room available. Plus, the receive data available (RDA) bit in the line status register (LSR) is set to signal that new data is received. This status bit is reset when data is read from RBR. If the receive buffer is full at the moment of receiving, the buffer overrun error (OE) bit is set in LSR.

For the transmitting function, there is also a hardware transmit holding register (THR), which is used to hold data before it is transmitted out. When this buffer

has room available, the transmit holding register empty (THRE) bit in LSR is set to signal the status. This status bit is reset when data is written into THR.

For RDA,OE or THRE, there is a corresponding interrupt, which will become pending when the status bit is set and if it is enabled. This is interrupt-driven operation. If interrupts are disabled, software must query LSR to check the status of the serial port. This is polling-based operation.

#### 3.2 Serial Port Model

I instantiate the abstract device as shown in Section 2.2.1 with a model for the serial port UARTO from an NXP LPC2129 chip [72]. This is a popular embedded processor based on the ARM7TDMI architecture. It targets industrial control applications. I call the model uart0.

My serial port model is conservative: while it does not model all behaviors of the real device, it should be the case that any code that is verified against the model will also work when running on the hardware. Table 3.1 summarizes the model's coverage of the serial port's register set, where LCR<sub>DLAB</sub> stands for divisor latch access bit which controls if registers DLL (divisor latch least significant byte) and DLM (divisor latch most significant byte) are accessible. It is the 7th bit in the LCR (line control register). My model omits modem functionality. Interrupts are not supported in this part of work, and will be supported later. In my model, the internal hardware receiving and transmitting buffers both have fixed size of 1. In LPC2129 the buffer sizes are configurable. It does not model line errors or wire encoding since it is a program model, and it is assumed that whole characters are transmitted. It does not model the break function.

In my model, a register access can lead the system into undefined states in the following scenarios:

- 1. When the register is not modeled. For example, access of the addresses reserved for the modem function is undefined.

- 2. When a write-only register is read, or when a read-only register is written.

- 3. When a reserved bit is written.

- 4. When data corruption may occur. For example the receiving buffer register is read when its value is indeterminate.

The state of such a serial port model is represented with a record:

```

<|RBR: bool[8]; THR: bool[8]; SCR: bool[8]; DLL: bool[8]; DLM: bool[8];

LCR<sub>DLAB</sub>: bool; LSR<sub>RDR</sub>: bool; LSR<sub>OE</sub>: bool; LSR<sub>THRE</sub>: bool; LSR<sub>TEMT</sub>: bool;

clock: num; in: num \rightarrow bool[8] option; out: num \rightarrow bool[8] option|>.

```

Here, byte is the type for 8-bit byte. num is the type for the natural number. Note that registers LCR and LSR (line status register) are broken down into Boolean flags. Access of FCR (FIFO control register) is modeled as side effect only. THR and out form the output queue, and RBR and in form the input queue.

One important feature is that the speed of the serial port is parameterized relative to the core speed. I am not modeling the exact baud rate, but in a similar fashion I use the 16-bit word value from DLM and DLL as a clock divisor b unless its value is zero, in which case b is set to be 1. For a serial port state ps,  $get\_divisor$  ps returns b. The serial port only performs meaningful state transition every b cycles. To do so, clock is incremented for each instruction cycle. It will be reset to zero when it reaches b, at the moment the device transmits and receives data, updates its registers, and shifts its input and output streams. At other moments when 0 < clock < b - 1, the serial port only updates clock for book-keeping purposes. However, memory-mapped accesses from the processor core can occur at any clock value. The effect of these accesses are visible when a new cycle begins.

The incoming and outgoing data streams are modeled as functions in and out from natural numbers to byte option. An option type has two constructors, THE and NONE. THE x wraps x into the particular option type, while NONE indicates nothing is wrapped, which is suitable to describe that at some moments the input or output stream are idle with no characters transmitted. With every b cycles of instruction execution, the two streams will shift. The new value for in is

$$\lambda t$$

. in  $(t+1)$ ,

and the new value for out is

$$\lambda t$$

. if  $t = 0$  then  $d$  else out  $(t - 1)$

where d is the character just sent out.

# 3.3 High-Level View of the Serial Port Behavior

I describe the high-level behavior of the serial port device in terms of strings extracted from the output queue and input queue. Only nonempty strings are considered. The predicates are defined in Figure 3.1. Suppose hd, tl return the first character and the tail of a string, respectively, and T stands for Boolean value true. Serial port states which are not well-defined are excluded by the uart\_wellform function. An input stream can be shifted by cutStream. For the transmit function, outString s os describes that s is the most recent string in the output stream os. sentString s ps describes that s is the most recent string sent out by the processor in the serial port state ps. For the receive function, inString s is describes that s is the string in the input stream s inputString s ps describes that s is the next string to be received by the processor in the serial port state s if no buffer overrun ever occurs. shifted s ps is a weak safety invariant for the receive function. It states that the RBR and income stream in state s resulted from s after some cycles of operation. inputStream s ps describes that s is the extended income stream of s in which RBR is appended at the head of the income stream if there is data in RBR.

For a serial port state ps, sentString  $s_{rx}$  ps associates its receive state with string  $s_{rx}$ , and sentString  $s_{tx}$  ps associate its transmit state with string  $s_{rx}$ . Using strings, it is intuitive to assert the behavior of the serial port driver. For example,  $s_{rx}$  does not change if there is no buffer overrun over an autonomous transition of the serial port.

## 3.4 Correctness of a Serial Port Driver

I started with a freely available driver for the LPC2129's UART0 that is implemented in C, and compiled it to ARM assembly using GCC 4.1.1. I made one change to the compiler's output, which was to change the "bx" instruction that implements a return-from-function to a "mov" instruction. I did this because "bx" is not modeled in the ARM tool that does not support the THUMB mode. I proved full correctness for three functions which interact with device registers: the putch function which transmits a character by writing it to THR, the getch function which attempts to read a character from RBR, and the getchwW function which performs a blocking

read from RBR. The code is shown in Figure 3.2.

#### 3.4.1 Serial Port Model Soundness

The correctness claim is based on the correctness claims of other components. I assume that the ARM model in HOL4 is correct (this ARM model has been used in several projects, and an earlier version was verified against a specific instance of the ARM hardware). Then I depend on the fact that the abstract device model attached to the ARM model is sound as shown in Section 2.3. The soundness of the serial port model is proved in the process. For example, I have proved the following properties regarding the transmitting and receiving functions, among others:

- 1. No character will be appended to the output under any of the following conditions:

- (a) no memory-mapped read or write occurs,

- (b) a read occurs,

- (c) a write occurs but the THR register is not accessible or not written, and the FCR register is not written (to reset the transmission queue).

In fact, the only way to append a character to the output is to write to the THR register when thre set. The theorem is shown in Figure 3.3.

- 2. The input string is not changed under any following conditions:

- (a) between two ticks of the serial port clock,

- (b) the serial port clock ticks, but there is no incoming character on the wire or the RBR is empty,

- (c) a memory-mapped write occurs, and the FCR register is not written (to reset the transmission queue),

- (d) a memory-mapped read occurs, and RBR is not read.

The only way to read the head of the string is to read the RBR when it is not empty. The theorem is shown in Figure 3.4.

### 3.4.2 Memory Safety and Control Flow Integrity

To prove the full correctness we need to prove memory safety and control flow integrity of the driver code. These properties are a useful part of the safety specification, and also are important for proof management. Memory safety requires that only a given range of registers in the ARM core and memory is accessed. This implies compliance to the calling convention. So it is useful when proving the callers of the driver functions. It also implies the separation of instruction memory, which is essential to prove control flow integrity.

Ideally, the addresses or registers accessed in an ARM instruction could be known when it is decoded. Here, I use a different approach by examining the change of content in the memory and registers:

```

sep_mem addrMap\ s_1\ s_2 \triangleq \forall\ x.\ addrMap\ x \Rightarrow (\ s_2.\mathsf{memory}\ (\mathsf{addr30}\ x) =\ s_1.\mathsf{memory}\ (\mathsf{addr30}\ x)), \mathsf{sep\_reg}\ regMap\ s_1\ s_2 \triangleq \forall\ x.\ regMap\ x \Rightarrow (s_2.\mathsf{regs}\ x = s_1.\mathsf{regs}\ x).

```

sep\_mem accSet s1 s2 checks two system states s1 and s2 to see if any address not in the set addrSet have the same content. sep\_reg regSet s1 s2 does the same thing for the registers across two states. Since the access which could cause side effects is limited to access of memory-mapped device registers, which is already taken care of, this approach serves our purpose well. However, these two predicates are rather naive, an embedding of separation logic here would have be cleaner.

Control flow integrity specifies that only certain sequences of PC values can occur in the execution. For example, when putch is busy waiting, it strictly follows the loop. Control flow integrity is necessary to prove the loop invariant, or generally any data flow, and thus helps us to sequentially compose the theorems about segments of the execution together to prove the final theorem. In the final theorem I did not include the stepwise specification of the control flow.

## 3.4.3 Correctness of the Serial Port Driver

I proved the full correctness theorems for three functions: putch, getch, and getchw. putch first waits for thre being set. It will then copy the byte from register r0 to THR. getch copies the byte from RBR to register r0 if  $LSR_{\rm RDR}$  is set. Otherwise it returns 0xff. getchw first waits for  $LSR_{\rm RDR}$  being set. It will then copy the byte from RBR to register r0. Note that if getchw is used to receive a string, characters may be dropped if the serial port is too fast.

The correctness property includes both liveness and safety properties. For all three functions, the basic liveness property states that the function will return to its caller. In addition, the basic safety property states that memory safety is observed, the operating configuration of the serial port device is not changed in terms of its speed (described by the slow-down factor) and the controlling bit LCR<sub>DLAB</sub>, and the system do not run into any erroneous state. Functional correctness is proved for putch, getch and getchw:

- 1. putch successfully appends the character from r0 to the string already sent out in the output queue. The basic safety and liveness properties hold in the process. The theorem is shown in Figure 3.5.

- 2. getch successfully reads a character from the input queue or return 0xff. The basic safety and liveness properties hold in the process. The theorem is shown in Figure 3.6.

- 3. If there is a string in the input queue, and the serial port is slow enough, the function getchw will successfully read the next character from the input stream. In the process, no overrun error occurs to the serial port, and the basic safety and liveness properties hold. The theorem is shown in Figure 3.7.

The correctness of getchw depends on the speed of the serial port device relative to the ARM core, and the latency caused by the driver code. The driver code must be efficient enough and the serial port must be slow enough so that no buffer overrun error can occur. My approach allows this constraint to be expressed, while the previous work does not [2]. The authors discussed receiver buffer overrun issue from a programmer's point of view and suggested three approaches. One of them is to do a worst case execution time (WCET) analysis of interrupt handler and the device driver and derive the latency in the processing of received data. The latency can be used to derive the maximum baud rate of the serial port.

However, the authors modeled the device like a thread concurrent to the processor, and did not introduce a clock to their serial port model. As a result, timing related properties such as buffer overrun cannot even be expressed in their model.

The tight timing properties in the theorem in Figure 3.7 will be helpful when proving the string-level receiving function, which calls **getchw** repetitively. The string

can be retrieved completely without overrun, as long as the interval between the consecutive return and entry of getchw is bounded by delay, which is bounded by the difference between the clock divisor of the serial port and the latency introduced in getchw, which is 9 instruction cycles. This guarantees that oe is not set when getchw is entered the next time, thus the precondition of getchw is met.

### 3.4.4 Proof Method