# ALGORITHMS FOR AUTOMATIC GENERATION OF RELATIVE TIMING CONSTRAINTS

by

Yang Xu

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

May 2011

Copyright © Yang Xu 2011

All Rights Reserved

## The University of Utah Graduate School

## STATEMENT OF THESIS APPROVAL

| e members:                                       |

|--------------------------------------------------|

| Shair 03/03/2011 Date Approved                   |

| Member $\frac{03/03/2011}{\text{Date Approved}}$ |

| Member $\frac{03/01/2011}{\text{Date Approved}}$ |

| Member 03/03/2011 Date Approved                  |

| Member $\frac{02/23/2011}{	ext{Date Approved}}$  |

| , Chair of                                       |

| / 1                                              |

and by Charles A. Wight, Dean of the Graduate School.

#### ABSTRACT

Asynchronous circuits exhibit impressive power and performance benefits over its synchronous counterpart. Asynchronous system design, however, is not widely adopted due to the fact that it lacks an equivalent support of CAD tools and requires deep expertise in asynchronous circuit design. A relative timing (RT) based asynchronous circuit design flow using traditional synchronous commercial CAD tools was recently proposed. This design flow enables engineers who are proficient in using synchronous design and CAD flow to more easily switch to asynchronous design without asynchronous experience while retaining the asynchronous benefits of power and performance. Relative timing constraints are the key step to this design flow, and were generated manually by the designer based on his/her intuition and understanding of the circuit logic and structure. This process was quite time-consuming and error-prone.

This dissertation presents an algorithm that automatically generates a set of relative timing constraints to guarantee the correctness of a circuit with the aid of a formal verification engine – Analyze. The algorithms have been implemented in a tool called ARTIST (Automatic Relative Timing Identifier based on Signal Traces).

Automatic generation of relative timing constraints relies on manipulation, such as searching and backtracking, of a trace status tableau that is built based on the counter example signal trace returned from the formal verification engine. The underlying mechanism of relative timing is to force signal ordering on the labeled transition graph of the system to restrict its reachability to failure states such that the circuit implementation conforms to the specification. Examples from a simple C-Element to complex six-four GasP circuits are demonstrated to show how this technique is applied to real problems.

The set of relative timing constraints generated by ARTIST is compared against the set of hand generated constraints in terms of efficiency and quality. Over 100 four-phase handshake controller protocols have been verified through ARTIST and Analyze. ARTSIT vastly reduces the design time as compared to hand generation which may take days or even months to achieve a solution set of RT constraints. The quality of ARTIST generated constraints is also shown to be as good as hand generation.

# CONTENTS

| $\mathbf{A}\mathbf{B}$ | BSTRACT                                                                                                                                                                                                                   | iii                              |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LIS                    | ST OF FIGURES                                                                                                                                                                                                             | viii                             |

| LIS                    | ST OF TABLES                                                                                                                                                                                                              | X                                |

| AC                     | CKNOWLEDGEMENTS                                                                                                                                                                                                           | xi                               |

| CH                     | HAPTERS                                                                                                                                                                                                                   |                                  |

| 1.                     | INTRODUCTION                                                                                                                                                                                                              | <b>1</b>                         |

|                        | 1.1.1 Handshake Protocol1.2 Timing1.2.1 Synchronous Clock                                                                                                                                                                 | 3<br>4<br>4                      |

|                        | 1.2.2 Delay Insensitivity1.2.3 Metric Timing1.2.4 Unit Delay                                                                                                                                                              | 5<br>6                           |

|                        | 1.2.5 Relative Timing1.3 Model Checking1.4 Contributions1.5 Dissertation Structure                                                                                                                                        | 7<br>7<br>8<br>10                |

| 2.                     | RELATIVE TIMING BASED DESIGN METHODOLOGY                                                                                                                                                                                  | 13                               |

|                        | 2.1 Relative Timing                                                                                                                                                                                                       | 13                               |

|                        | Clocked CAD Tools  2.2.1 Formal Verification of Asynchronous Templates  2.2.2 Template Characterization  2.2.3 Mapping to Backend  2.2.4 Postlayout Timing Validation  2.3 Verifying Compositional Asynchronous Protocols | 15<br>16<br>18<br>22<br>22<br>23 |

| 3.                     | FORMAL VERIFICATION ENGINE                                                                                                                                                                                                | 33                               |

|                        | 3.1 Modeling Concurrent System Using CCS 3.2 Labeled Transition System                                                                                                                                                    | 33<br>34<br>36                   |

| 4.            | AUTOMATING CONSTRAINT GENERATION                                    | <b>40</b>      |

|---------------|---------------------------------------------------------------------|----------------|

|               | 4.1 Past Work 4.2 Formal Definitions 4.2.1 Computation Interference | 41<br>43<br>43 |

|               | 4.2.2 Nonconformance                                                | 45<br>47       |

|               | 4.3 Common Feature of Hazards                                       | 48             |

|               | 4.4 Generating Relative Timing Constraints                          | 50             |

|               | 4.5 Trace Status Tableau                                            | 51             |

|               | 4.5.1 State                                                         | 52             |

|               | 4.5.2 Number of Transitions                                         | 53             |

|               | 4.5.3 Enabling and Causal Relations                                 | 54             |

|               | 4.5.4 Locating Failure                                              | 55             |

|               | 4.6 Relative Ordering                                               | 55             |

|               | 4.7 POD Backtracking                                                | 57             |

| <b>5</b> .    | CASE STUDY                                                          | 71             |

|               | 5.1 Simple C-element                                                | 71             |

|               | 5.2 Six-Four GasP Circuit                                           | 75             |

|               | 5.2.1 Introduction to GasP                                          | 75             |

|               | 5.2.2 Converting Single Track to Double Track                       | 76             |

| 6.            | RESULTS                                                             | 100            |

|               | 6.1 Efficiency                                                      | 100            |

|               | 6.2 Quality                                                         | 101            |

| 7.            | CONCLUSION AND FUTURE WORK                                          | 110            |

|               | 7.1 Conclusion                                                      | 110            |

|               | 7.2 Future Work                                                     | 111            |

| $\mathbf{RF}$ | EFERENCES                                                           | 113            |

# LIST OF FIGURES

| 1.1  | Four-phase handshaking protocol                                                        | 12 |

|------|----------------------------------------------------------------------------------------|----|

| 1.2  | Two-phase handshaking protocol                                                         | 12 |

| 2.1  | Relative timing application to clocked system                                          | 25 |

| 2.2  | Circuit diagram to demonstrate path-based relative timing constraint                   | 25 |

| 2.3  | Applying $b+ \prec a-$ to state transition graph                                       | 26 |

| 2.4  | Relative timing based asynchronous design flow                                         | 26 |

| 2.5  | Example design: a simple ASIC mathematical pipeline segment computing out $= x^2 + 3x$ | 27 |

| 2.6  | Top level Verilog for latch based implementation example                               | 28 |

| 2.7  | LC circuit implementation                                                              | 28 |

| 2.8  | Verilog implementation of linear controller                                            | 29 |

| 2.9  | CCS specification of linear controller                                                 | 29 |

| 2.10 | Gate library to CCS specification mapping                                              | 29 |

| 2.11 | CCS implementation of linear controller                                                | 29 |

| 2.12 | Three deep pipeline of linear controller                                               | 30 |

| 2.13 | Minimized specification of linear controller                                           | 30 |

| 2.14 | An example of data check                                                               | 30 |

| 2.15 | Timing report of constraint $lr+ \Rightarrow rr+ \prec y-\dots$                        | 31 |

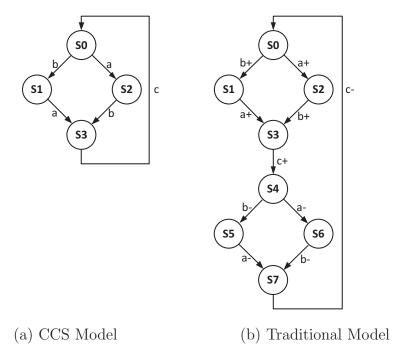

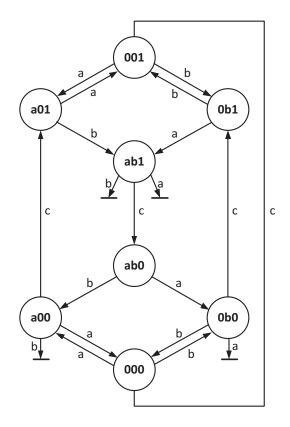

| 3.1  | State space difference between CCS and traditional model of a C-element.               | 39 |

| 3.2  | Demonstration of labels and colabels of internal transition $\tau$                     | 39 |

| 3.3  | Semimodular CCS specification of a 2-input NAND gate                                   | 39 |

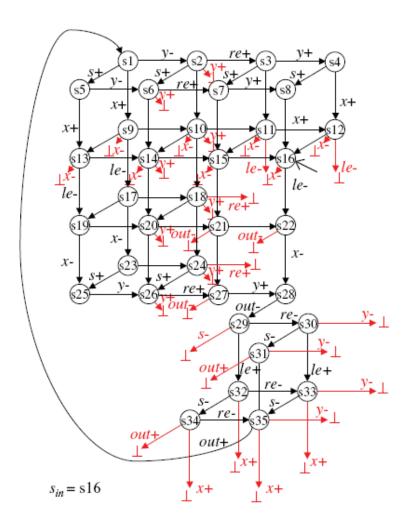

| 4.1  | Partial state graph of GasP circuit                                                    | 60 |

| 4.2  | Semi-modular state transition graph of 2-input NAND gate                               | 61 |

| 4.3  | An example of flattened STG                                                            | 61 |

| 4.4  | An illustration for deadlock                                                           | 62 |

| 4.5  | Template graph for mapping failure points                                              | 62 |

| 4.6  | Top level algorithm of ARTIST                                                          | 63 |

| 4.7  | Algorithm for constructing the cell of trace status tableau                            | 63 |

| 4.8  | Algorithm for generating next state                                                    | 64 |

| 4.9  | Timing graph of unrolling representation of signal transition for clocked system             | 64 |

|------|----------------------------------------------------------------------------------------------|----|

| 4.10 | Algorithm for generating transition count                                                    | 65 |

| 4.11 | Algorithm for generating Enabled bit                                                         | 65 |

| 4.12 | Algorithm for generating Failed bit                                                          | 65 |

| 4.13 | A demonstration of failure transition                                                        | 66 |

| 4.14 | An example to illustrate the strength of relative orderings                                  | 66 |

| 4.15 | Algorithm for generating failure transition                                                  | 66 |

| 4.16 | Algorithm for generating current state                                                       | 66 |

| 4.17 | Algorithm for generating previous state                                                      | 67 |

| 4.18 | Algorithm for generating enabling transition                                                 | 67 |

| 4.19 | Algorithm for generating dynamic set                                                         | 67 |

| 4.20 | Algorithm for generating point-of-divergence                                                 | 67 |

| 4.21 | Algorithm for generating full causal list of transitions                                     | 68 |

| 4.22 | Algorithm for matching POD                                                                   | 69 |

| 5.1  | C-element symbol                                                                             | 86 |

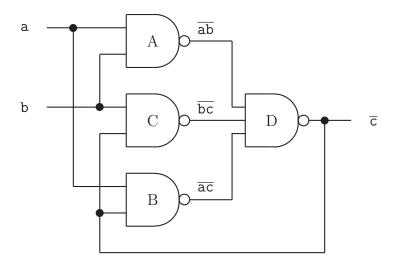

| 5.2  | C-element implemented with three 2-input and one 3-input NAND gates.                         | 86 |

| 5.3  | CCS implementation of C-element                                                              | 86 |

| 5.4  | Partial state graph mapped from trace status tableau                                         | 87 |

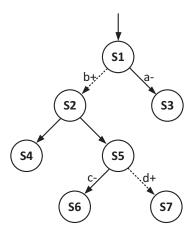

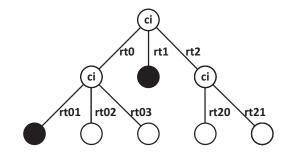

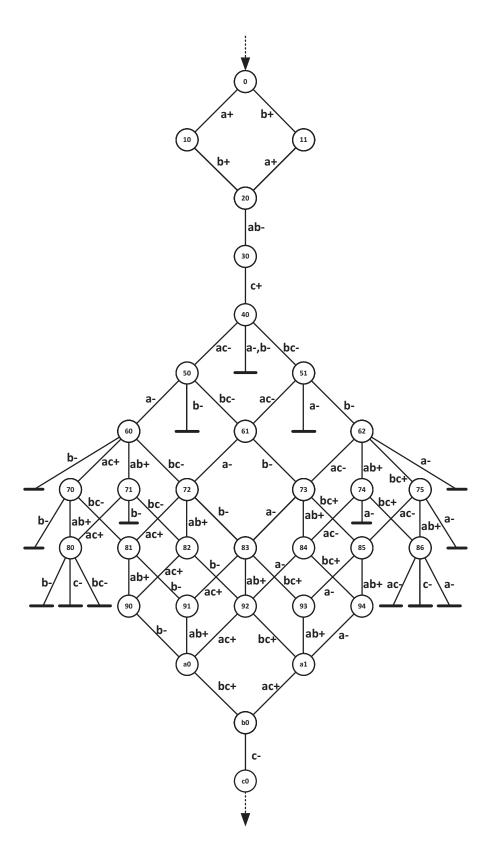

| 5.5  | Tree of relative timing constraints                                                          | 87 |

| 5.6  | Six-Four basic GasP circuit                                                                  | 87 |

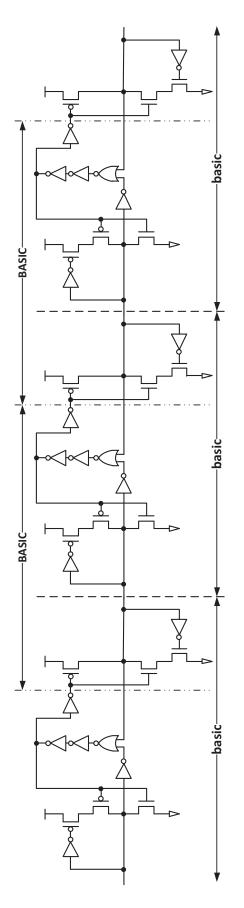

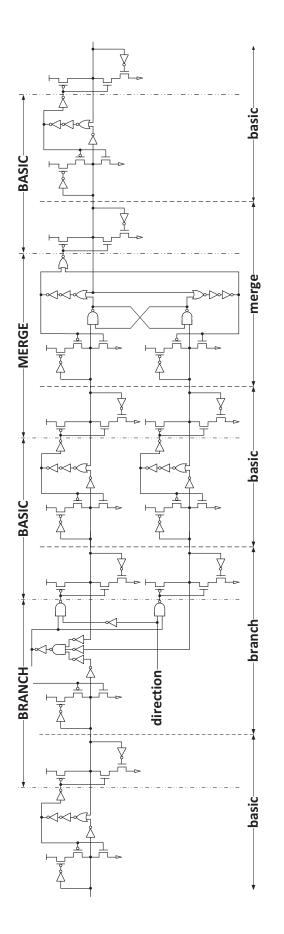

| 5.7  | Repartition of 3 deep GasP pipeline                                                          | 88 |

| 5.8  | Repartition of a simplified switch network composed by basic, branch and merge GasP circuits | 89 |

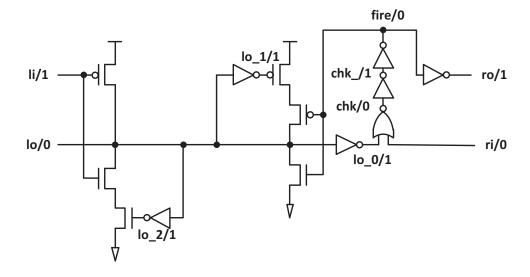

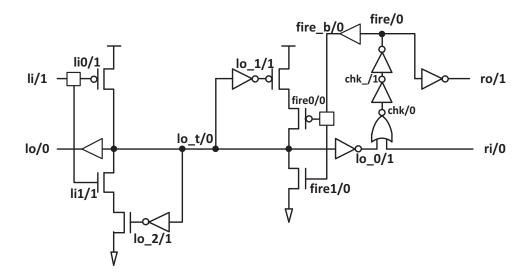

| 5.9  | Speed-independent model of repartitioned double track GasP basic circuit.                    | 90 |

| 5.10 | Delay-insensitive model of repartitioned double track GasP basic circuit.                    | 90 |

| 5.11 | Specification of double track GasP circuit                                                   | 90 |

| 5.12 | Speed-independent implementation of double track GasP circuit                                | 91 |

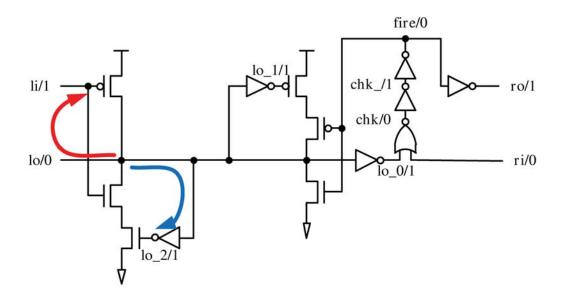

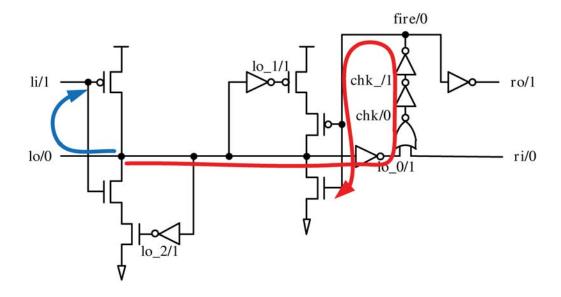

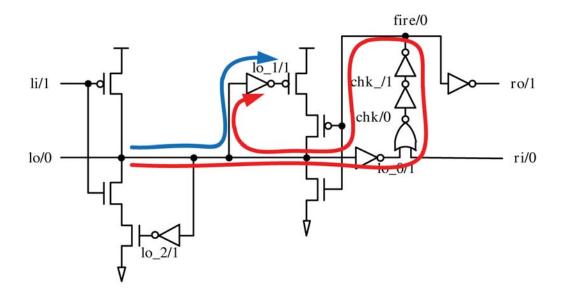

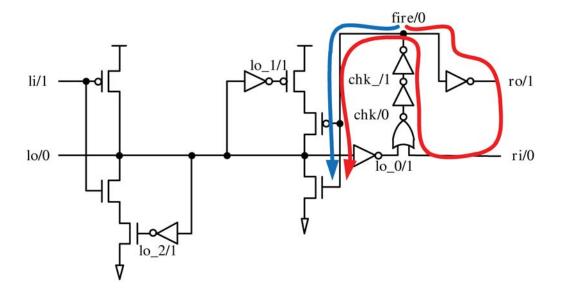

| 5.13 | GasP speed-independent verification RT0                                                      | 91 |

| 5.14 | GasP speed-independent verification RT1                                                      | 92 |

| 5.15 | GasP speed-independent verification RT2                                                      | 92 |

| 5.16 | GasP speed-independent verification RT3                                                      | 93 |

| 5.17 | GasP speed-independent verification RT4                                                      | 93 |

| 5.18 | GasP speed-independent verification RT5                                                      | 94 |

| 5.19 | GasP speed-independent verification RT6  | 94  |

|------|------------------------------------------|-----|

| 5.20 | GasP speed-independent verification RT7  | 95  |

| 5.21 | GasP speed-independent verification RT8  | 95  |

| 5.22 | GasP speed-independent verification RT9  | 96  |

| 6.1  | CCS definition of $LC_{max}$             | 105 |

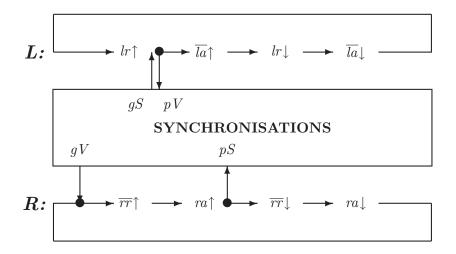

| 6.2  | Synchronization between L and R channels | 105 |

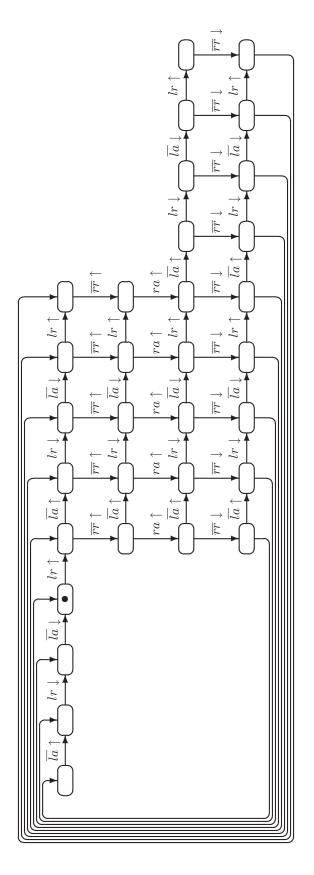

| 6.3  | State graph of $LC_{max}$                | 106 |

| 6.4  | State transition graph of C-element      | 107 |

# LIST OF TABLES

| 2.1 | CCS specification functional descriptions                                                           | 32  |

|-----|-----------------------------------------------------------------------------------------------------|-----|

| 2.2 | RT constraints for linear controller                                                                | 32  |

| 2.3 | Set_data_check constraints of linear controller                                                     | 32  |

| 2.4 | Cycle cutting constraints                                                                           | 32  |

| 4.1 | An example of trace status table                                                                    | 70  |

| 5.1 | Truth table of C-element                                                                            | 97  |

| 5.2 | Signal transition mapping of CCS, logic level and unrolling count representations.                  | 97  |

| 5.3 | An example tableau for an error trace in verification of C-element                                  | 97  |

| 5.4 | Full causal paths of relative ordering events                                                       | 97  |

| 5.5 | Complete solution sets of RT constraints                                                            | 98  |

| 5.6 | Speed-independent set of RT constraints for 6-4 basic GasP circuit                                  | 99  |

| 6.1 | Four-phase protocol verification results                                                            | 108 |

| 6.2 | Unoptimized RT constraints and corresponding traces versus hand-generate constraints for C-Element. |     |

#### ACKNOWLEDGEMENTS

I would like to thank my advisor Dr. Ken Stevens who brought me into the asynchronous world. With his trust, I can continue his favorite research topic on relative timing. Relative timing is the key hub of all the other research in his group. I feel so honored that my work can be applied to others' research. I appreciate all he has done for me, either for work or my family. During this research, I was experiencing the most difficult period I have ever had in my life due to a family emergency. Without his encouragement and care, I could not have made it. This work could not have been done without his guidance, help and patience.

I also would like to thank Marly Roncken, who was the industrial liaison from Intel on SRC project and now is the director of Asynchronous Research Center (ARC) of Portland State University, for her support and help on this relative timing work and instructing me regarding GasP circuit verification. Thank you to Anping He and Professor Xiaoyu Song from Portland State University for the great idea and help in the collaboration on GasP circuit verification.

Next I would like to thank Dr. Chris Myers, Ganesh Gopalakrishnan and Priyank Kalla for their suggestions on related work, and background references. I also would like to thanks Vikas Vij who provided his preliminary results for cycle cutting algorithms to me. Thanks for the funding by grant 1424.001 from Semiconductor Research Corporation (SRC).

Finally I would like to thank my parents, Liangui and Suhua, who have been standing behind me and encouraging me, providing as much as they can do, and especially taking care of my son during the period I am in difficulties. Thanks to my wife, Jingwen, for bringing our son Oscar into this colorful world.

#### CHAPTER 1

## INTRODUCTION

The modern integrated circuit (IC) industry continues to develop extraordinarily fast as predicated by Moore's Law. The number of transistors that can be placed on an integrated circuit doubles approximately every two years. Billions of transistors can be integrated into a single die. The transistors are no longer expensive, and are now almost free.

This miracle depends largely on the use of flip-flops and a clocked synchronous design and verification methodology. This methodology employs a single clock signal as a global timing reference for all the components. Further, the industry standard clocked CAD tools for automating design and verification greatly reduce the time to market. Most engineers focus on register transfer level (RTL) design and verification and are released from complex back-end jobs which are performed mainly by EDA tools.

Design reuse allows heterogeneous IP cores to be integrated on a single system on chip (SoC) to reduce design time. More recently multicore processors are successfully designed and fabricated to increase the capability of parallel computing by multithread programming.

However, there are many problems with today's synchronous circuit design.

- Power consumption. The design consumes more power as the clock periodically switches. Even fine-grained clock gating may not be enough, especially for handheld devices. Modern mobile handset chip manufacturers like Apple, Qualcomm and Broadcom seek low power solutions and finally turn to use low power ARM based architectures.

- Performance. The performance of SoC and multicore processors rely on how efficiently the multiple cores are designed and communicate. The inefficient

design of a switch fabric may degrade the performance of the chip. As the price of transistors goes down, wires become more expensive since they occupy more space, consume more power, and become a major source of delay. This motivates more research on interconnect fabrics and network-on-chip [1].

This dissertation proposes a design methodology targeting 3x improvement on performance and power with asynchronous design over its synchronous counterpart. Timing assumptions of a design usually result in simpler low power and high speed circuits. In this research, relative timing is the key timing methodology employed in an asynchronous design flow using traditional clocked CAD tools not only to guarantee the correctness of the circuits but to drive timing driven synthesis, place and route and postlayout timing validation. Hence generating a correct set of relative timing constraints becomes the key step of this design methodology. This dissertation formally describes the algorithm for automatic generation of relative timing constraints as a replacement of traditional hand generation, which may take an experienced designer days or even months to figure out a complete set of constraints. This algorithm is implemented in a tool called ARTIST (Automatic Relative Timing Identifier based on Signal Traces) and applied to a bunch of asynchronous circuits. The results show that ARTIST can automatically generate a complete set of relative timing constraints in an extremely shorter time while retaining the same quality of constraints compared to traditional hand generation.

## 1.1 Asynchronous Circuit

Asynchronous circuits are not a new technology, but a resurgence to the semiconductor industry. Asynchronous circuit design has a long history. The research in asynchronous design can be traced back to the mid 1950s [2, 3]. Recently, industry and academia show increased interest in asynchronous design due to power and performance issues as design is getting more complex.

Asynchronous design has the following advantages over synchronous design [4]:

• Low power consumption. Asynchronous design consumes less power than synchronous counterpart because of zero standby power consumption [5, 6].

- High performance. Synchronous design operates at a clock frequency that is

determined by the worst-case delay of combinational logic between flip-flops.

Asynchronous design, which employs handshaking, operates at actual delay. It

is reactive and does not need to wait for a clock edge to proceed.

- No clock distribution and clock skew problems. Asynchronous design employs handshaking protocol for communication instead of the global clock signal.

However, there are drawbacks to asynchronous circuit design that vastly restrict its wide adoption. Unlike synchronous design, asynchronous design lacks uniform CAD tools. Some companies that have succeed in asynchronous circuit design have their own design flow and tools as proprietary properties and not open to the public. Without the aid of tools, asynchronous design still involves much manual work, such as custom layout. This greatly increases the difficulties in asynchronous design. Asynchronous design also requires designers to have experience and expertise in asynchronous circuit design.

The International Technology Roadmap for Semiconductors predicted that 20% of designs will be driven by handshake clocking in 2012, rising to 40% by 2020 [7]. To achieve this target, it is imperative to have some asynchronous design flow that can implement handshake clocking using available clocked CAD tools while requiring little experience of asynchronous design.

#### 1.1.1 Handshake Protocol

Asynchronous design employs handshake protocols instead of using a global reference clock. Communication between asynchronous components is implemented by sending request and receiving acknowledgment signals.

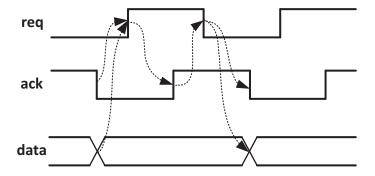

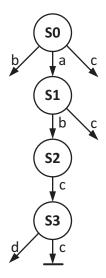

Handshaking protocols can be classified as two-phase and four-phase protocols with respect to a handshake cycle. The four-phase handshaking protocol is implemented by initiating data and asserting request signal. The receiver absorbs the data and asserts acknowledge. The sender de-asserts request upon receiving acknowledge. Finally the receiver de-asserts acknowledge. Another handshake may start if the sender detects that acknowledge is de-asserted. Figure 1.1 shows the transition

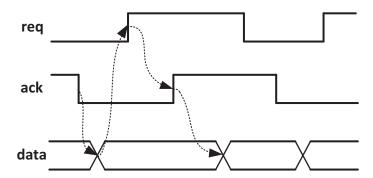

relationships of request and acknowledge signals. The handshaking request and acknowledge signals return to zero after one handshaking cycle is finished. The 4-phase handshake protocol is also called return-to-zero (RTZ) signaling or level signaling. The 2-phase handshake protocol shown in Figure 1.2 uses transition signaling instead. The handshaking signals do not return to their initial value after one handshaking cycle is finished. So 2-phase handshake protocol is also called non-return-to-zero (NRZ) signaling or transition signaling.

The 4-phase return-to-zero handshake protocol takes extra transitions to finish a handshake cycle but results in simpler logic implementation. The simple 4-phase circuits can be faster and lower power than 2-phase circuits due to their simplicity. The 2-phase non-return-to-zero handshake protocol theoretically leads to faster designs, but the resulting circuits are more complex.

The handshaking protocol can be implemented completely independent of the data path. This is called a bundled data protocol. The request and acknowledge signals are one bit signals. On the other hand, the request signal can be encoded into data signals. One simple example is the dual rail protocol where the request and one data bit are encoded with two signal wires.

# 1.2 Timing

Timing is an inherent quality and correctness aspect of circuit and protocol design, whether the designs are clocked or asynchronous. A circuit will not work correctly without functionality and timing correctness. Modern digital circuit design relies heavily on the timing methodology it employs. The following sections describes the synchronous timing and four most often used asynchronous timing methodologies in both industry and academia.

#### 1.2.1 Synchronous Clock

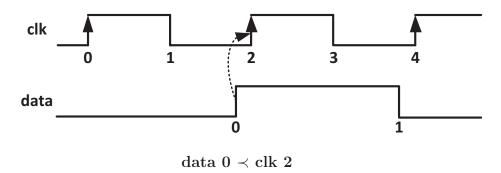

Modern digital IC design favors a synchronous design methodology. In synchronous design, all the components are synchronized by a global clock. It is normally implemented by a employing banks of flip-flops with combinational logic between

them. Flip-flops are edge sensitive storage elements and on every positive or negative edge of clock the flip-flop the input data is sampled.

The clock frequency is determined by the worst delay of the combinational logic between flip-flops. The setup and hold time must be satisfied in order to ensure that the data is correctly latched.

Global clock synchronization and industry standard CAD tools allow engineers to design digital circuits at the behavior level. However, as the design becomes more complex, power, performance and clock distribution become a big issue for synchronous design.

#### 1.2.2 Delay Insensitivity

Delay-insensitive (DI) circuits operate correctly independent of the delay of logic gates and wires. The delay insensitive methodology is the most robust of all asynchronous circuit timing methodologies. However, due to limitations, it is not practical to create delay insensitive systems since it results in larger, slower and power hungry circuits than similar timed circuits [9, 10].

As a practical alternative, quasi-delay-insensitive (QDI) circuits are invariant to the delays of gates and wires, with the exception that certain wires are required to be isochronic forks with identical delays. Of all useful asynchronous design styles, QDI circuits make the fewest timing assumptions, as only the isochronic fork is assumed. There are many successful QDI designs including TITAC from Tokyo Institute of technology [11, 12], MiniMIPS from Caltech [13] and SPA from the University of Manchester [14] among others.

Delay insensitive circuits integrate asynchronous handshaking control logic into data path. All handshaking is implemented with data communication, which is different from a bundled data protocol where the control logic path and data path are separate. A change in sampled data may indicate a start of handshaking. This is implemented by data encoding, normally in the format of a 1-of-n code [15]. Dual-rail encoding is the simplest encoding for delay-insensitive design. It encodes the request signal with the data and uses two wires per data bit for validity or empty.

#### 1.2.3 Metric Timing

Although quasi-delay-insensitive design is tolerant to environmental variation, its conservative timing results in high complexity circuits. Another approach utilizes metric timing constraints to generate timed asynchronous circuits, which result in less circuit complexity.

This approach unfolds the cyclic graph of the specification into an infinite acyclic graph and uses metric timing assumptions to remove the redundancy in the specification and thus results in a finite subgraph for a simpler implementation [16, 17].

The metric timing specifies upper and lower bounds on the delay between signal events becoming enabled and firing [18, 19]. It requires the designer to estimate the min-max delay in a reasonable range such that it meets the accurate delay extracted from postlayout parameters. Further, the impact that a change to the delay of a single component has on the correct behavior of a system as a whole cannot be known by an engineer, making design changes (ECO: Engineering Change Orders) more difficult to perform without re-running the verification.

#### 1.2.4 Unit Delay

The timing of an asynchronous circuits can be analyzed by counting the number of gate delays in a path based on the assumption that all logic gates have the same uniform delay. This is a very straightforward and intuitive way to design and analyze aggressive self-resetting asynchronous circuits such as GasP family circuits [20]. After the circuit is logically verified, the transistors must be properly sized to yield unit delays to meet the assumptions made for correct behavior of the circuit. The method of calculating transistor widths with the aid of logical effort [21] analysis to generate unit delay is presented in [22]. The unit delay model facilitates prelayout timing validation, but the procedure of characterizing transistor sizes is relatively more complex and requires back-end experience and a lot of manual work. However sizing transistor to yield unit delay over-constrains the circuits and degrades their potential performance and power.

#### 1.2.5 Relative Timing

Relative timing is a timing methodology that constrains the firing order of two events based on logic path delays. It fits perfectly into a state based formal verification methodology such that by enforcing relative timing constraints, failure states are made unreachable. Unlike other methods, necessary timing assumptions become explicit when using relative timing. Designers can visualize, reason about, and manipulate path based timing constraints. Enhanced path based relative timing constraints restrict the overall delay of two paths from a common causal point of divergence (POD) to a common point of convergence (POC) to have a specified order of arrival.

One of the advantages of relative timing over other timing methodologies is that path based relative timing constraints can be supported by conventional clocked CAD tools for timing driven synthesis, place and route and pre and postlayout timing validation. A relative timing based design methodology enables synchronous design engineers to switch to asynchronous circuit design using their familiar tools without having too much knowledge of asynchronous circuits.

## 1.3 Model Checking

Simulation based validation methodologies have been the main stream for validating complex CMOS integrated circuits. However, as design is getting more and more complicated, simulation based validation is not enough to cover all possible scenarios. One cannot enumerate all the possible cases necessary for verification, and some corner cases remain unevaluated. Such a situation is not acceptable, especially for safety critical products. A design must be exhaustively verified. An example of such a failure is the Ariane 5 rocket, which exploded less than 40 seconds after launching.

Model checking is a technique for verifying finite state concurrent systems [23]. Model checking performs an exhaustive reachability analysis of the state space to find any violations of specified properties. Whenever a property is not satisfied, a counter example is returned.

To perform model checking, a design must be modeled in a formal representation which is accepted by the model checker. The specification is a list of properties to be checked against the design. The process of modeling checking is automatic. When model checking fails, an error trace is returned. This helps the designer to locate and debug the errors.

The properties are normally specified using temporal logics. CTL\* formulas describe the properties of computation trees and are composed of path quantifiers and temporal operators. The path quantifiers can be **A** and **E** only where **A** means for *all* computation paths and **E** means for *some* computation path. The temporal operators can be **X** (next time), **F** (finally), **G** (globally), **U** (until) and **R** (release). Temporal logics are often classified into two sublogics, one of which is linear time logic that describes the properties along a single computation path and the other is branching time logic that describes the properties over all the paths that are possible from the current state. An example property specifying the mutual exclusion of two events can be described by temporal logic  $\mathbf{G}(\neg e_1 \vee \neg e_2)$ .

The main challenge of model checking is state explosion, especially for verifying concurrent systems with lots of concurrency. Symbolic representations for state transition graphs helps mitigate the state explosion problem. Many symbolic representations are based on ordered binary decision diagrams (OBDD) [24]. A BDD represents a boolean formula where each node is a boolean variable and its two outcoming edges denotes if the boolean variable evaluates to true or false. It consists of two terminal nodes called the 0-terminal and 1-terminal. A path from the root to the 1-terminal means that the boolean function is evaluated to be true. The basic idea is from Shannon expansion. The size of a BDD is determined by the ordering chosen for the variables. Finding an optimal ordering of variables is normally not feasible. Hence heuristics are employed for finding a relatively good variable ordering [25, 26]. How to apply formal verification to real world hardware design problems by using PSL [27] or SystemVerilog [28] is described in [29].

#### 1.4 Contributions

The key contributions of this research is automatic formal generation of a complete set of path based relative timing constraints for correctness of circuits and enables clocked CAD flow for asynchronous circuit design. The algorithm for automatic generation of relative timing constraints vastly reduces design time, which may take days or even months for an experienced asynchronous designer to figure out a complete set of relative timing constraints by hand based on the designer's intuition and expertise on circuit structure and knowledge on asynchronous design. Our one push of button tool ARTIST simply returns a solution set of relative timing constraints and does not require the user to know anything specific to the design. This research may bring up large adoption of asynchronous design by employing clocked CAD tools without expertise in asynchronous circuit knowledge.

As the key step of the asynchronous design flow using conventional clocked CAD tools, the efficiency of constraint generation directly affects the design time of this flow. Without a complete set of relative timing constraints all the subsequent steps by using clocked CAD tools such as timing driven synthesis, place and route and postlayout timing validation cannot be performed.

This work also drives the correct cycle cutting. Inefficient cycle cutting where the relative timing constraints related critical timing paths may be broken results in unexpected power hungry circuits. Given a complete set of relative timing constraints generated from this research work, the synthesis and place and route engines are dictated to remain those relative timing constrained paths intact.

The research work described in this dissertation also has the ability to allow user to specify the desired common timing reference to facilitate postlayout timing validation. Postlayout timing validation is an important step in both clocked and asynchronous design which checks if constrained timing holds with extracted parasitic parameters. To perform timing validation, a virtual clock pin must be specified as a common causal reference to evaluate the delays of two timing paths. This virtual clock pin might be mapped to a primary input, invisible internal or primary output signal. This dissertation supports flexible common causal points since it returns all possible point of divergences. Normally the request signal as a primary input signal is mapped into this virtual clock pin. However in case of repartition the circuit hierarchy to facilitate verification such as verifying GasP, an internal signal may be required to

work as the virtual clock signal. User specified point of divergence allows the user to specify desired signal as the common timing reference.

This work also supports unrolling count representation of signal transition where the fall or rise behavior of a transition is modeled using transition counts instead of logic levels. This representation is used for multicycle constraints and especially useful when specifying any relative timing constraint related to clock.

#### 1.5 Dissertation Structure

The dissertation is structured as follows.

Chapter 2 introduces a relative timing based asynchronous design and verification methodology. The relative timing concept is formally defined in Section 2.1. This design methodology allows designers to use traditional clocked CAD tools to design asynchronous circuits. It is implemented by characterizing asynchronous control templates and then mapping the relative timing constraints into sdc constraints such that they are compatible with clocked tools for timing driven synthesis, place and route and pre and postlayout timing validation. A scalable verification method for verifying large compositional asynchronous handshaking protocol using industry symbolic model checking engines is described in Section 2.3.

Chapter 3 describes the formal verification engine employed in this asynchronous design methodology. The formal models for model checking uses the process language Calculus of Communicating System (CCS). The fundamental structure this formal verification relies on and how the formal verification detects internal glitches and check conformance between the implementation and specification are described.

Chapter 4 presents the algorithms for automatic generation of relative timing constraints which is the key work of this thesis. The past work and its weaknesses are described. All types of errors returned from the formal verification engine are formally defined and analyzed. Then the data structure employed for generating relative timing constraints and the key algorithms are described.

Chapter 5 shows a simple C-Element example to demonstrate how the algorithms work on a real example. Another example, 6-4 GasP circuit, demonstrates how

the single track signaling design can be converted to a formal verification engine compatible double track signaling.

Chapter 6 compares the results generated by ARTIST against hand generation in terms of efficiency and quality.

Chapter 7 concludes this dissertation work and addresses possible future work.

Figure 1.1. Four-phase handshaking protocol.

Figure 1.2. Two-phase handshaking protocol.

#### CHAPTER 2

# RELATIVE TIMING BASED DESIGN METHODOLOGY

### 2.1 Relative Timing

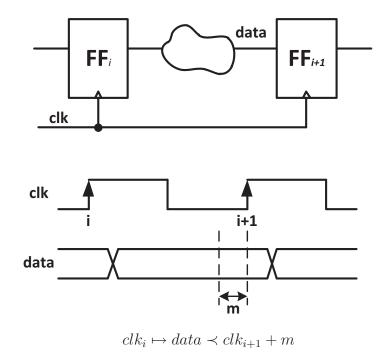

Relative timing is an innovative timing methodology that enables aggressive asynchronous circuit design and verification. It constrains the design by enforcing the firing ordering of two events such that timing failures are made unreachable. Relative timing is applicable to clocked design as well. The setup time constraint of the flip-flop that the data have to be stable at least setup time before the clock edge is triggered is a relative timing constraint as shown in Figure 2.1.

**Definition 2.1** A Relative Timing Constraint specifies a required signal ordering that results from system timing that is imposed between two events that share a common timing reference.

The behavior of a logic component generally depends on the combinational pattern of input and output values. The state space may be exponential with respect to the number of inputs and outputs. However, in the real operating scenario not all possible sequences will happen. Thus the environment always restricts the behavior of logic components to a subset of the whole. If one can figure out relative timing constraints on inputs that models the environment, the resulting circuit after synthesis can be much simpler than the one that implements the complete set of behaviors [30, 31]. For asynchronous handshake protocol design, relative timing assumptions result in concurrency reduction since the assumption on relative ordering of inputs and outputs makes the protocol more sequential.

Relative timing can be used as a timing constraint for verification. A set of relative timing constraints can make a circuit implementation hazard-free and behave as the specification requires.

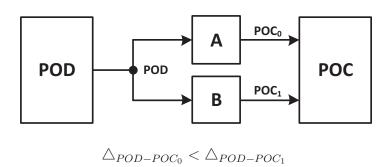

When relative timing concept was first proposed, the format of a relative timing consisted only of an ordering of two events such as  $a \prec b$ , which specifies event a occurs before event b. As a timing assumption that specifies the firing order of primary inputs, this format is enough to represent the environment behavior. However specifying the relative ordering of two events for verification is not enough because this format cannot be supported by timing analysis engines for postlayout timing validation. The enhanced format of relative timing adds a point-of-divergence (POD) onto the relative ordering to form path-based timing constraints that are able to be validated in postlayout static timing analysis engines. A path-based relative timing constraint is represented as POD  $\mapsto$  POC<sub>0</sub>  $\prec$  POC<sub>1</sub>. Figure 2.2 interprets the meaning of this representation - the delay of the path from POD to POC<sub>0</sub> is less than the delay of the path from POD to POC<sub>1</sub>, i.e.,  $\triangle_{POD-POC_0} < \triangle_{POD-POC_1}$ . Block POD and POC represents logic gates and block A and B represents either logic gates or just wires.

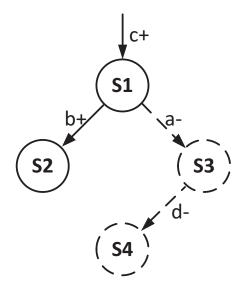

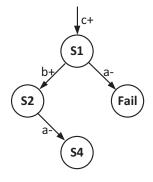

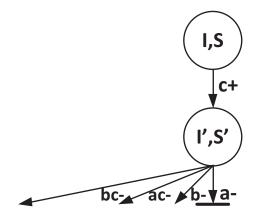

Relative timing is more straightforward, especially when the system is modeled as a state transition graph. Given a particular state that has concurrent transitions (have two or more egress transitions whereas a state that has only one egress transition is deterministically sequential), a relative timing constraint enforces a design to always choose the path with a smaller delay. The subgraph directed from the longer path will be never reachable. Figure 2.3 illustrates how the relative timing constraint impacts the state transition graph. If the relative ordering  $b+ \prec a-$  is applied to the partial graph in Figure 2.3 and then the subgraph in dashed line is no longer reachable. Note that the relative timing constraint is not truncating a graph but makes the partial graph unreachable.

# 2.2 Asynchronous Design Flow Using Clocked CAD Tools

Asynchronous circuits, albeit impressive in power and performance benefits compared to clocked circuits, is not widely adopted mainly because of the lack of supporting CAD tools and requiring deep expertise in asynchronous circuit design knowledge.

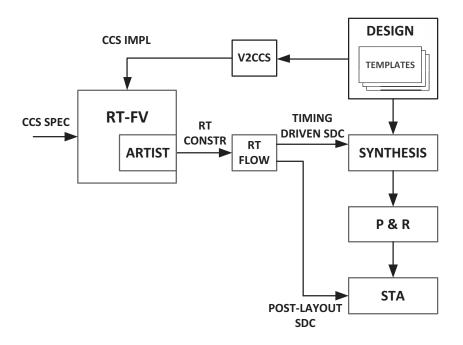

Rather than compete in the CAD domain and develop distinctly independent design flows, a relative timing based design methodology is proposed that exploits traditional commercial CAD tools to facilitate asynchronous circuit design and verification [32]. The design flow is shown in Figure 2.4. This design and verification methodology allows the designer to apply commercial clocked CAD as much as possible. This approach consists of two major procedures: asynchronous template characterization and traditional system design that employs precharacterized templates.

Once the asynchronous templates are fully characterized, synchronous designers can use them as library cells to build a system by following clocked design flow. This enables designers who have been working on synchronous design to switch to asynchronous circuit design smoothly with little expertise in the asynchronous domain.

This design flow applies to all kinds of asynchronous circuit designs, including desynchronization. Desynchronization is a process of converting synchronous circuit into an asynchronous one [33, 34, 35]. To desynchronize a synchronous design, its clock tree is replaced with handshake controllers, but the combinational logic between registers in the data path remains untouched. This replacement perfectly fits the bundled data protocol, which separates the control path and data path.

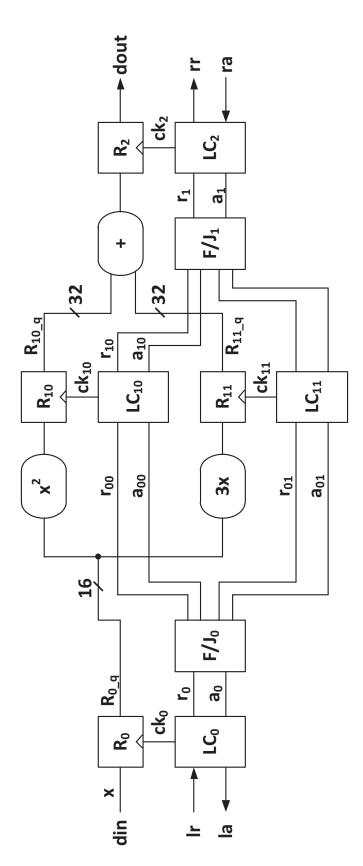

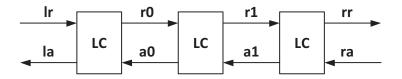

A simple example of desynchronization shown in Figure 2.5 will be used to demonstrate the asynchronous design flow in detail. It is a pipelined design that implements the function of  $x^2 + 3x$  where a 16-bit wide data path forks x out to upper and lower data paths performing multiplications concurrently and then joining the paths to perform an addition operation. The control path is composed of linear controllers (LC) and fork join (F/J) modules. This linear controller implements a four-cycle return-to-zero handshake protocol. This is a timed protocol and follows the burst mode assumption that assumes that the circuit stabilizes before any new inputs can

be accepted [36, 37]. The data path is composed of registers (R), either flip-flops or latches. The oval boxes represent arithmetic operations. The top level Verilog code for a latch based implementation is shown in Figure 2.6.

#### 2.2.1 Formal Verification of Asynchronous Templates

Formal verification and relative timing constraint generation of asynchronous templates are the key steps of the design flow. Templates refer to the local asynchronous controllers that can be instantiated one or multiple times for building a system. Formal verification is the process of creating a complete set of relative timing constraints that guarantee the correctness of a template.

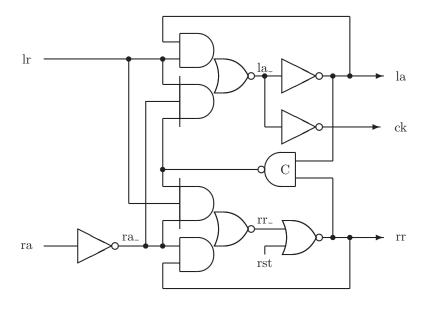

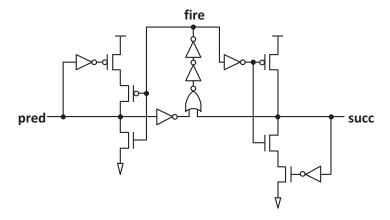

The asynchronous templates in the example are the linear controller and the fork-join modules. The circuit diagram of the linear controller is shown in Figure 2.7 and its Verilog representation is shown in Figure 2.8.

The template is formally verified in an untimed manner that assumes unbounded delay on both gates and wires by a bisimulation relation based formal verification engine. Thus the circuit implementation and specification are required to be modeled with formal representations which can be recognized by the formal verification engine. The Calculus of Communicating System (CCS) [38] is selected as the process language for the formal model because it formally supports verification of nondeterminism such as arbiters and synchronizers by its distinct support for invisible internal  $\tau$  transitions. The CCS specification of the linear controller is shown in Figure 2.9. A Verilog netlist can be converted into a formal CCS model automatically by a tool called verilog2ccs which is the V2CCS block shown in Figure 2.4. This tool takes three input files and outputs the CCS implementation of the circuit.

- A structural Verilog file that consists of primitive gates as the implementation of the template. See Figure 2.8.

- A mapping file of Verilog gates to formal semi-modular description of each gate in CCS. See Figure 2.10.

- A functional description of the gates in the target technology. See Table 2.1.

The converted CCS implementation of the linear controller is shown in Figure 2.11. The tool also has the ability to calculate the initial semi-modular state of each gate, i.e., the initial value of inputs and outputs of each gate. For example, A121O2I0bc01 defines initial values of lr, ra, y, la and la to be 0, 1, 1, 0 and 1 respectively.

Untimed model checking is then performed between the circuit implementation and specification, which is the RT-FV block shown in Figure 2.4. The first run of formal verification performs speed-independent verification that assumes unbounded delay on gates and zero delay on wires. This generally results in numerous violations, many of which are due to technology mapping. These violations may cause internal glitches that may finally propagates to the primary outputs and result in failure of the design. Relative timing constraints must be generated to remove these violations by restricting the reachability of failure states with circuit timing. By applying the relative timing constraints to the implementation recursively, the design conforms to the specification. The set of relative timing constraints for timing driven sizing and place and route. The set of relative timing constraints for the speed-independent run on this linear controller is shown in the SI rows of Table 2.2.

The second run of formal verification is verification of the timing properties of the template protocol. Some protocols are timed protocols that may not accept all signal behaviors of its environment. Protocol verification is performed to verify that the interaction between local templates is correctly performed. For a linear pipeline, three of the same templates can be composed in series as shown in Figure 2.12. For other generic asynchronous systems, protocol verification at the system level requires the templates to be composed as specified. Instead of using the plain specification of templates, protocol verification requires minimized specification which can be generated from Concurrency Work Bench (CWB) [39] with the *min* command. The minimized specification of the linear controller is shown in Figure 2.13. The set of relative timing constraints generated for the second run are key constraints for timing driven sizing and place and route as well which is shown in the Protocol row of Table 2.2.

A third verification run is performed to generate any timing constraints between the handshake clocking and the datapath logic. Like clocked design, handshake clocking follows the same setup constraint – data has to be stable at least some setup time before the relevant handshaking signal is triggered, e.g.,  $lr\uparrow \mapsto din \prec la\uparrow$ . When a design that employs the bundled data protocol is synthesized, such constraints create a matched delay between the datapath and control logic. This is guaranteed by constraining that the minimum relative delay of the control path to be larger than the maximum delay of data path. This set of relative timing constraints is key for timing driven synthesis and place and route of creating matched delay in the pipeline.

The final verification run performs delay insensitive verification, which not only assumes unbounded delay on gates but also wires. The wire fork is not isochronic any more. It is modeled with an unbounded delay in an arbitrary order on the two branching wires. Delay insensitive verification is necessary for some asynchronous circuits that makes use of wire delays to achieve extremely aggressive timing to maximize throughput, such as GasP family circuits. The set of relative timing constraints for delay-insensitive verification is shown in the DI row of Figure 2.2.

A template is fully characterized with a complete set of relative timing constraints generated by the above four rounds of verification runs. The process of generating relative timing constraints can be manually done based on designer's strong knowledge of asynchronous circuits and his/her understanding of the circuit structure of the design under test. It is quite time-consuming and prone to errors. Generating a complete set of relative timing constraints for a design may take an experienced designer hours or even days. The objective of this dissertation is to present a method that can automatically generate relative timing constraints that are a key part of this design flow.

#### 2.2.2 Template Characterization

After a complete set of relative timing constraints is derived, the design enters RT flow phase where template characterization and mapping relative timing constraints to backend are performed.

The set of relative timing constraints for template characterization is required to be mapped into compatible sdc constraints such that they can be supported by conventional CAD tools for timing driven synthesis, place and route and postlayout timing validation.

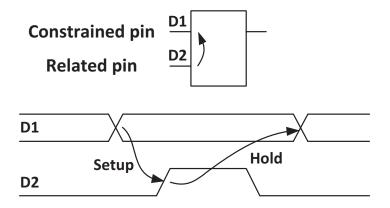

Synopsys tools support setup and hold constraint checking between two data signals where neither of them is a clock signal. This is implemented with set\_data\_check command. But its fundamental principle is similar to clock based setup and hold checks which assume one of the data signals is considered as a clock pin, called the related pin, while the other is regarded as traditional data, called the constrained pin. A data check example is shown in Figure 2.14. The related pin D2 is regarded as a reference clock pin and the constrained data is checked for setup and hold violation according to the reference. The set\_data\_check command takes a value that specifies a setup or hold time for which D1 must be stable before or after D2 goes high. The options of command set\_data\_check is shown below.

#### command set\_data\_check

race\_margin

-clock

-from | -rise\_from | -fall\_from related\_pin

-through traverse\_pin

-to | -rise\_to | -fall\_to constrained\_pin

-setup | -hold

Since CAD is designed for clocked design, a -clock argument is always an option of this command as a common reference point. The -clock option in set\_data\_check specifies the starting point to related and constrained pins such that the delays of the two paths are qualified for comparison. Asynchronous design has no clock signal and thus a virtual clock signal must be specified. The point-of-divergence of path based relative timing constraints exactly fits the -clock option. In asynchronous design, this virtual clock pin is normally mapped to a request signal. The related and constrained timing paths can be specified using the -from and -to options. The shorter path of a relative timing constraint uses the -from option, and longer path uses -to option followed by the specific pin names. More concretely, the transition behaviors of the two racing events of relative timing constraints can be modeled by -rise\_from,

-fall\_from, -rise\_to and -fall\_to options. Generally there is more than one path available for evaluation, and the CAD tool may not report the exact one wanted. In such a case the -through option is used to specify the pin points the desired path passes through. The options -setup and -hold are mutually exclusive. Only one of them will appear in the single sdc constraint. The command set\_data\_check is mostly used for postlayout timing validation.

The sets of relative timing constraints in speed-independent, protocol and delay-insensitive verifications are all mapped into set\_data\_check constraints, which is shown in Table 2.3.

The storage elements in the data path, using either flip-flops or latches, still need to obey setup and hold constraints. If combinational logic exists between pipeline stages for data processing, the processed data normally takes more time to propagate to the storage element of the next stage. On the other hand, in the control path pipeline, handshaking is performed much faster than the data path and thus the signal ordering and setup time cannot be guaranteed. Hence delay elements must be added into the control path to match data path delay such that the data is guaranteed to be available when handshake clocking arrives. This is implemented by a pair of commands – set\_max\_delay and set\_min\_delay as shown below.

#### command set\_min/max\_delay

delay\_value

-from | -rise\_from | -fall\_from start\_pin

-to | -rise\_to | -fall\_to end\_pin

Set\_max\_delay command is used to constrain the data path while set\_min\_delay command is used to constrain the control path. The delay from the output of previous stage data storage element to the input of next stage storage element is constrained by set\_max\_delay by a delay value such that the delay of combinational logic between them must have a maximum delay of that value. Likewise the set\_min\_delay constrains the control path to have the minimal given delay value. Since both commands specify end-to-end delay, option -from and -to are enough to denote the starting and end pins. The following example set\_min/max\_delay constraints constrain the maximum delay from register bank R0 to R10 to be 1.7ns and the minimum delay from the linear

control associated with R0 to the linear control associated with R10 to be 1.7ns as well. This guarantees that the data always arrive before the control signal.

The synthesis and place and route tools may automatically optimize circuits, such as merging back-to-back inverters, combining multiple simple primitive gates into a complex gate or vice versa. This modification breaks the original structure and characteristics of the asynchronous templates and introduces unexpected timing hazards. The command set\_size\_only prevents the logic structure of the templates from being modified by the CAD tools, and only allows the tools to optimize the drive strength of the gates to gain better power and performance. Another command, set\_dont\_touch, disallows the tool from modifying the design in any manner. The hierarchical components of templates should be constrained by one of these two commands. The following constraint disallows any structural modification on the AOI gate of linear controller.

```

set_size_only -all_instances { */lc3 }

```

Clocked CAD tools operate on directed acyclic graphs (DAGs) for timing driven optimization. Once a cycle is found in timing graphs, the CAD tools will invoke built-in algorithms to break the cycle. The users can also define how and where to break the cycle using set\_disable\_timing by themselves. Asynchronous sequential circuits inherently have cycles in the design due to its sequential characteristics. The handshake protocols themselves also produce cycles. These cycles must be cut to be compatible with the CAD tools. The built-in cycle cutting algorithm of clocked CAD tools may be good enough for clocked design. However, the timing driven synthesis and place and route require the relative timing constraints to be successfully applied to the design and need all relative timing constraints related timing paths to remain unbroken. This requires that the paths from point-of-divergence to point-of-converge

of the relative timing constraints are forbidden to being cut. Hence custom cycle cutting algorithms are necessary. An algorithm for automatic cycle cutting, as part of this asynchronous design flow, is being developed. The set\_disable\_timing constraint is applied to primitive gates and the timing arc is removed from the specified input pin (-from option) to the specified output pin (-to option). In this example, both local cycles and handshake cycles are cut as shown in Table 2.4.

The set of relative timing constraints from the speed-independent run and min/max constraints are key constraints for timing driven sizing and place and route. The set of constraints for protocol verification do not usually need to be included in synthesis and place and route because of the magnitude of slack between the two race paths. The set of relative timing constraints from the delay-insensitive run is not used for synthesis but used for postlayout timing validation.

#### 2.2.3 Mapping to Backend

The relative timing constraints must be mapped to backend format of constraints with full hierarchical path names.

An enhanced format of sdc constraint allows the mixed use of module names and instance names in defining hierarchical port names [40]. Variables are also supported to be specified in hierarchical port names to reduce tediously duplicating constraints for each instantiated templates. This is used to map timing constraints generated for an asynchronous design template into its instances used in a design.

#### 2.2.4 Postlayout Timing Validation

Timing validation using standard static timing analysis engines is employed to guarantee that the constrained timing holds with extracted parasitic parameters. All the relative timing constraints that are either applied to timing driven synthesis and place and route as well as the delay-insensitive constraints are required for performing postlayout timing. The report\_timing command is used to return a detailed timing report for each constraint by listing all the nodes the path passes through and their corresponding delays. The necessary constraint settings for the relative timing constraint  $lr+ \Rightarrow rr+ \prec y-$  are shown below. Figure 2.15 shows the related timing

report. The timing report lists details the delay information of the two paths from the point-of-divergence to the point-of-convergence and compares the total delay to see if constrained timing holds.

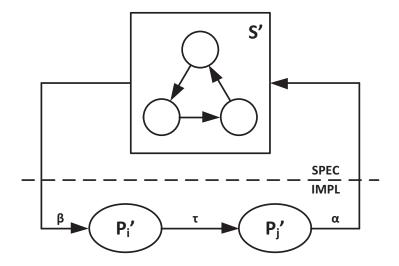

## 2.3 Verifying Compositional Asynchronous Protocols

This system level design methodology incorporates the composition of multiple precharacterized asynchronous handshake protocols. System level verification is employed to check any violations in the communication of these protocols. Each protocol may be a timed protocol, which must be constrained to be compatible with its adjacent environmental behavior. The timing required to specify environmentally friendly behaviors is implemented by relative timing constraints.

System level formal verification is perform to guarantee the correct interactions of local protocols. The state explosion problem has been a primary challenge of formal model checking specially for asynchronous circuits and protocols where much concurrency exists. The explicit state based formal verification engine such as *Analyze* may not be applicable to relatively large and complex design.

A scalable verification methodology for compositional asynchronous hardware protocols uses mature symbolic model checking engines [41] to mitigate the state explosion issue during verification [42]. First, the a state graph based representation of the protocols is upgraded to an extended state graph with their timed relative timing property constraint information. The relative timing constraints are represented by making use of a relative timing variable where the variable is set when the point-of divergence fires and reset when the shorter path point-of-convergence signal transition

fires. The longer path point-of-convergence signal transition can fire only after the variable is reset. Hence the formal model of protocol and corresponding relative timing constraint is derived from this extended state graph. Second, properties such as safety, liveness, and semimodularity are generated. Finally symbolic model checking is performed by the industry symbolic engine NuSMV. If the properties specified are satisfied, the composed protocols can interact correctly. If this fails, a counter example is reported and further investigation must be performed to guarantee if missing relative timing constraints exist.

This methodology allows us to verify larger designs that are composed of heterogeneous timed asynchronous handshake protocols using relative timing and symbolic model checking techniques more efficiently.

Figure 2.1. Relative timing application to clocked system.

Figure 2.2. Circuit diagram to demonstrate path-based relative timing constraint.

Figure 2.3. Applying  $b+ \prec a-$  to state transition graph.

Figure 2.4. Relative timing based asynchronous design flow.

Figure 2.5. Example design: a simple ASIC mathematical pipeline segment computing out =  $x^2 + 3x$ .

```

module apipeline (din, dout, lr, la, rr, ra, rst);

input lr, ra, rst;

output la, rr;

input [15:0] din;

output [31:0] dout;

reg [31:0] R0, R10, R11, R2;

assign dout = R2_q;

always @(*)

R0 = din;

linear\_control

(.ck(ck0), .lr(lr), .la(la), .rr(r0), .ra(a0), .rst(rst));

lc0

latch_active_high

R0\_reg

(.d(R0), .clk(ck0), .q(R0_q));

bcast_fork

bcf0

(.bi(r0),.bo0(r00),.bo1(r01),.ji0(a00),.ji1(a01),.jo(a0));

always @(*)

R10 = R0_q * R0_q;

linear\_control

lc10

(.ck(ck10), .lr(r00), .la(a00), .rr(r10), .ra(a10), .rst(rst));

latch_active_high

R10_reg

(.d(R10), .clk(ck10), .q(R10_q));

always @(*)

R11 = R0_q * 3;

linear\_control

lc11

(.ck(ck11), .lr(r01), .la(a01), .rr(r11), .ra(a11), .rst(rst));

latch_active_high

R11_reg

(.d(R11), .clk(ck11), .q(R11_q));

bcast\_fork

bcm0

(.bi(a1),.bo0(a10),.bo1(a11),.ji0(r10),.ji1(r11),.jo(r1));

always @(*)

R2 = R10_q + R11_q;

linear\_control

(.ck(ck2), .lr(r1), .la(a1), .rr(rr), .ra(ra), .rst(rst));

lc2

latch_active_high

R2_reg

(.d(R2), .clk(ck2), .q(R2_q));

endmodule // apipeline

```

Figure 2.6. Top level Verilog for latch based implementation example.

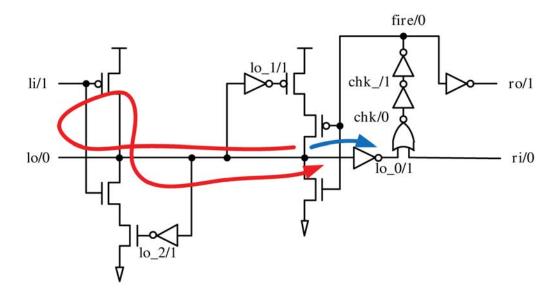

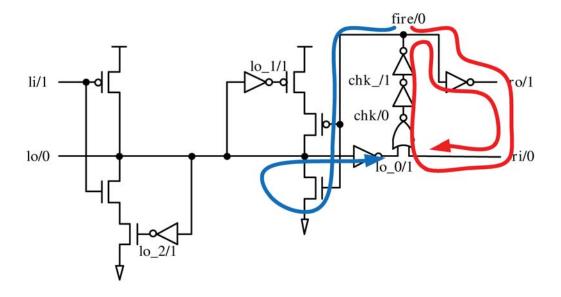

Figure 2.7. LC circuit implementation.

```

module linear_control (lr, la, rr, ra, ck, rst);

input

lr, ra, rst;

output

la, rr, ck;

(.A1(lr), .A2(ra_{-}), .A3(v_{-}), .B1(lr), .B2(la), .Y(la_{-}));

AOI32X2A12TH

lc0

AOI32X2A12TH

(.A1(lr), .A2(ra_{-}), .A3(y_{-}), .B1(ra_{-}), .B2(rr), .Y(rr_{-}));

lc1

NOR2X2A12TH

lc2

(.A1(la), .A2(rr), .Y(y_{-}));

(.A1(la<sub>-</sub>), .Y(la));

INVX2A12TH

lc3

INVX2A12TH

lc4

(.A1(la_{-}), .Y(ck));

NOR2X2A12TH

lc5

(.A1(rst), .A2(rr_{-}), .Y(rr));

INVX2A12TH

lc6

(.I(ra), .Y(ra_{-}));

endmodule // linear_control

```

Figure 2.8. Verilog implementation of linear controller.

```

L = lr.c1.'la. c2.lr.'la. L

R = 'c1.'rr.'c2.ra.'rr.ra.R

SPEC = (L | R) \ {c1, c2}

```

Figure 2.9. CCS specification of linear controller.

Figure 2.10. Gate library to CCS specification mapping.

Figure 2.11. CCS implementation of linear controller.

Figure 2.12. Three deep pipeline of linear controller.

```

SPEC*POMOMO

lr.SPEC*POMOM1

+ 'la.SPEC*POMOM3

SPEC*POMOM1

'rr.SPEC*POMOM2

SPEC*POMOM3

'rr.SPEC*POMOM4

SPEC*POMOM4

lr.SPEC*POMOM5

ra.SPEC*POMOM6

SPEC*POMOM6 =

'rr.SPEC*POMOM10 +

lr.SPEC*POMOM13

SPEC*POMOM13 =

'rr.SPEC*POMOM14 + 'la.SPEC*POMOM12

SPEC*POMOM12 =

'rr.SPEC*POMOM11 +

lr.SPEC*POMOM17

SPEC*POMOM17 =

'rr.SPEC*POMOM8

SPEC*POMOM8 =

ra.SPEC*POMOM1

SPEC*POMOM11 =

lr.SPEC*POMOM8

ra.SPEC*POMOMO

SPEC*POMOM14 =

'la.SPEC*POMOM11 +

ra.SPEC*POMOM16

SPEC*POMOM16 =

'la.SPEC*POMOMO

SPEC*POMOM10 =

lr.SPEC*POMOM14 +

ra.SPEC*POMOM15

lr.SPEC*POMOM16

SPEC*POMOM15 =

SPEC*POMOM5 =

'la.SPEC*POMOM9

ra.SPEC*POMOM13

SPEC*POMOM9

lr.SPEC*POMOM7

ra.SPEC*POMOM12

SPEC*POMOM7

ra.SPEC*POMOM17

SPEC*POMOM2 =

'la.SPEC*POMOM4

```

Figure 2.13. Minimized specification of linear controller.

Figure 2.14. An example of data check.

Startpoint: tk0\_lc3/A1 (clock source 'tk0/lr')

Endpoint:  $tk0\_lc3$  (falling edge-triggered data to data check

clocked by tk0/lr)

Path Group: tk0/lr Path Type: max

| Point                               | Incr   | Path   |

|-------------------------------------|--------|--------|

| clock tkO/lr (rise edge)            | 0.00   | 0.00   |

| clock source latency                | 0.00   | 0.00   |

| tkO_lc3/A1 (AOI32X1A12TH)           | 0.00   | 0.00 r |

| tkO_lc3/Y (AOI32X1A12TH)            | 0.27 * | 0.27 f |

| tkO_lc4/Y (NOR2X8A12TH)             | 0.11 * | 0.38 r |

| U243/ECK (FRICGXOP5BA12TH)          | 0.15 * | 0.53 r |

| U244/Y (BUFHX1P4A12TH)              | 0.07 * | 0.60 r |

| U245/Y (DLY2X0P5A12TH)              | 0.14 * | 0.74 r |

| U246/Y (DLY4X0P5A12TH)              | 0.58 * | 1.32 r |

| tkO_lc3/B1 (AOI32X1A12TH)           | 0.00 * | 1.32 r |

| data arrival time                   |        | 1.32   |

| clock tkO/lr (rise edge)            | 0.00   | 0.00   |

| clock source latency                | 0.00   | 0.00   |

| tkO_lc3/A1 (AOI32X1A12TH)           | 0.00   | 0.00 r |

| tkO_lc3/Y (AOI32X1A12TH)            | 0.26 * | 0.26 f |

| tkO_lc4/Y (NOR2X8A12TH)             | 0.11 * | 0.20 r |

| U243/ECK (FRICGX0P5BA12TH)          | 0.15 * | 0.52 r |

| U244/Y (BUFHX1P4A12TH)              | 0.07 * | 0.60 r |

| U245/Y (DLY2X0P5A12TH)              | 0.14 * | 0.74 r |

| U246/Y (DLY4X0P5A12TH)              | 0.58 * | 1.31 r |

| tkO_lc5_c_element2/Y (NAND2X1A12TH) | 0.13 * | 1.44 f |

| tkO_lc5_c_element3/Y (NAND3X1A12TH) | 0.10 * | 1.54 r |

| U1130/Y (INVX2A12TH)                | 0.05 * | 1.59 f |

| tkO_lc3/A2 (AOI32X1A12TH)           | 0.00 * | 1.59 f |

| data check setup time               | -0.05  | 1.54   |

| data required time                  |        | 1.54   |

| data required time                  |        | 1.54   |

| data arrival time                   |        | -1.32  |

| dana allivat nime                   |        | 1.02   |

| slack (MET)                         |        | 0.22   |

Figure 2.15. Timing report of constraint  $lr+ \Rightarrow rr+ \prec y-$ .

Table 2.1. CCS specification functional descriptions.

| CCS Cell Name        | SigIndex | Output | Function            |

|----------------------|----------|--------|---------------------|

| function NAND0001    | 4        | d      | not(a * b * c)      |

| function NOR001      | 3        | С      | not (a + b)         |

| function A2B1O2I0001 | 7        | d      | not((not(a)*b) + c) |

| function O12A2I0001  | 6        | d      | not(a * (b + c))    |

Table 2.2. RT constraints for linear controller.

| Category | RT Constraints                     |

|----------|------------------------------------|

| SI       | $lr+ \Rightarrow y \prec la-$      |

| 51       | $ m lr+ \Rightarrow y \prec rr-$   |

| Protocol | $lr+ \Rightarrow ra \prec la+$     |

|          | $ m lr+ \Rightarrow lr- \prec rr+$ |

|          | $lr+\Rightarrow la-\prec y$        |

|          | $ m lr+ \Rightarrow rr- \prec y$   |

| DI       | $lr+ \Rightarrow y + \prec lr-$    |

|          | $lr+\Rightarrow y+ \prec ra$       |

|          | $lr+ \Rightarrow rr \prec rr-$     |

Table 2.3. Set\_data\_check constraints of linear controller.

| Category | RT Constraints                                                            |

|----------|---------------------------------------------------------------------------|

| SI       | set_data_check -fall_from */lc1/A2 -fall_to */lc1/B1 -setup \$race_margin |

|          | set_data_check -fall_from */lc3/A2 -fall_to */lc3/B1 -setup \$race_margin |

| Protocol | set_data_check -fall_from */lc1/A1 -rise_to */lc1/B1 -setup 0             |

|          | set_data_check -fall_from */lc3/A1 -rise_to */lc3/B1 -setup 0             |

|          | set_data_check -fall_from */lc5/A -rise_to */lc5/Y -setup 0               |

|          | set_data_check -fall_from */lc5/B -rise_to */lc5/Y -setup 0               |

| DI       | set_data_check -rise_from */lc3/A2 -fall_to */lc3/A1 -setup 0             |

|          | set_data_check -rise_from */lc1/A2 -fall_to */lc1/A1 -setup 0             |

|          | set_data_check -fall_from */lc4/A -fall_to */lc4/Y -setup 0               |

Table 2.4. Cycle cutting constraints.

| Category  | Constraints                                              |

|-----------|----------------------------------------------------------|

| Local     | set_disable_timing -from A2 -to Y [find -hier cell *lc1] |

|           | set_disable_timing -from B1 -to Y [find -hier cell *lc1] |

|           | set_disable_timing -from A2 -to Y [find -hier cell *lc3] |

|           | set_disable_timing -from B1 -to Y [find -hier cell *lc3] |

| Handshake | set_disable_timing -from A1 -to Y [find -hier cell *lc1] |

|           | set_disable_timing -from A1 -to Y [find -hier cell *lc3] |

|           | set_disable_timing -from B0 -to Y [find -hier cell *lc3] |

## CHAPTER 3

# FORMAL VERIFICATION ENGINE

The formal verification engine employed in this design flow is an explicit state verification engine [43]. It is an untimed verification engine that does reachability analysis using all possible delay scenarios. The verification engine takes an implementation I, optionally a specification S, and a set of relative timing constraints C which is initially empty and outputs an error trace when there is a violation of a semimodular constraint or nonconformance between the implementation and the specification.

# 3.1 Modeling Concurrent System Using CCS

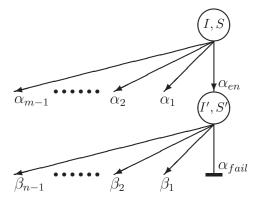

To use formal tools, both the specification and circuit implementation need to be modeled in a modeling language specific to the formal tool. There are many good modeling languages that are widely used today such as CSP [44, 45] and Petri-net [46]. The formal verification engine used for this research uses Calculus of Communication System (CCS) as the modeling language.

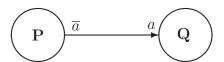

CCS is powerful for modeling concurrent systems. CCS can model very complex parallel systems only using five constructions and six transition rules. CCS syntax does not distinguish logic levels of signal transitions. Thus the state space used for modeling a system can be less than a traditional one where logic levels are specified. Figure 3.1 shows a comparison between a CCS model and a traditional model of a C-element. The CCS model in Figure 3.1(a) has four states, whereas the traditional model in Figure 3.1(b) has eight states. Therefore CCS modeling always results in half the state space as a traditional formal model for this design. In addition, CCS has the ability to model hierarchy. Local blocks can be modeled separately as CCS agents that are composed into a higher level design. It also supports silent internal actions

that make autonomous communications between agents. CCS is rich in equational reasoning as well.

CCS syntax contains five constructions.

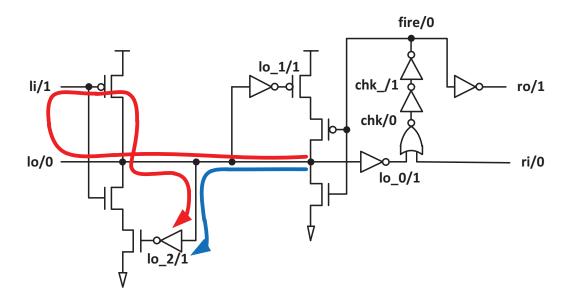

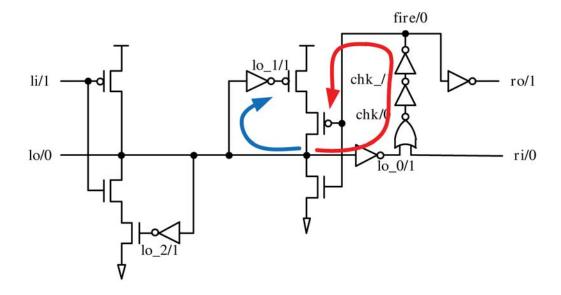

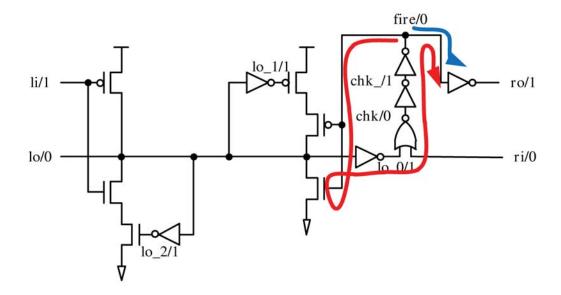

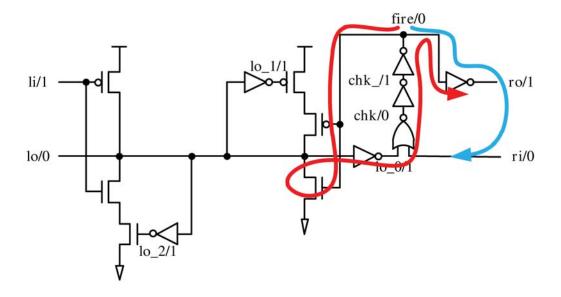

- **Prefix** specifies sequential behavior between two events, or an event followed by a process, using the prefix operation ".". For example,  $\alpha.\beta$  means that if event  $\alpha$  occurs it must be followed by the event  $\beta$ .  $\alpha.P$  means that once event  $\alpha$  occurs then process P is true.