# DESIGN AND OPTIMIZATION OF HARDWARE ACCELERATORS FOR DEEP LEARNING

by Ali Shafiee Ardestani

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

School of Computing The University of Utah May 2018 Copyright © Ali Shafiee Ardestani 2018 All Rights Reserved

### The University of Utah Graduate School

### STATEMENT OF DISSERTATION APPROVAL

The dissertation of Ali Shafiee Ardestani

has been approved by the following supervisory committee members:

Date Approved

| Rajeev Balasubramonian , | Chair(s) | 4 Aug 2017                               |

|--------------------------|----------|------------------------------------------|

| Alan Davis               | Member   | Date Approved  4 Aug 2017  Date Approved |

| Erik Brunvand            | Member   | 4 Aug 2017 Date Approved                 |

| Mahdi Nazm Bojnordi ,    | Member   | 4 Aug 2017 Date Approved                 |

| Vivek Srikumar ,         | Member   | 4 Aug 2017                               |

by <u>Ross T. Whitaker</u>, Chair/Dean of the Department/College/School of <u>Computing</u> and by <u>David B. Keida</u>, Dean of The Graduate School.

### **ABSTRACT**

Deep Neural Networks (DNNs) are the state-of-art solution in a growing number of tasks including computer vision, speech recognition, and genomics. However, DNNs are computationally expensive as they are carefully trained to extract and abstract features from raw data using multiple layers of neurons with millions of parameters. In this dissertation, we primarily focus on inference, e.g., using a DNN to classify an input image. This is an operation that will be repeatedly performed on billions of devices in the datacenter, in self-driving cars, in drones, etc. We observe that DNNs spend a vast majority of their runtime to runtime performing matrix-by-vector multiplications (MVM). MVMs have two major bottlenecks: fetching the matrix and performing sum-of-product operations.

To address these bottlenecks, we use in-situ computing, where the matrix is stored in programmable resistor arrays, called crossbars, and sum-of-product operations are performed using analog computing. In this dissertation, we propose two hardware units, ISAAC and Newton.In ISAAC, we show that in-situ computing designs can outperform DNN digital accelerators, if they leverage pipelining, smart encodings, and can distribute a computation in time and space, within crossbars, and across crossbars. In the ISAAC design, roughly half the chip area/power can be attributed to the analog-to-digital conversion (ADC), i.e., it remains the key design challenge in mixed-signal accelerators for deep networks. In spite of the ADC bottleneck, ISAAC is able to out-perform the computational efficiency of the state-of-the-art design (DaDianNao) by 8x. In Newton, we take advantage of a number of techniques to address ADC inefficiency. These techniques exploit matrix transformations, heterogeneity, and smart mapping of computation to the analog substrate. We show that Newton can increase the efficiency of in-situ computing by an additional 2x. Finally, we show that in-situ computing unfortunately cannot be easily adapted to handle training of deep networks, i.e., it is only suitable for inference of already-trained networks. By improving the efficiency of DNN inference with ISAAC and

Newton, we move closer to low-cost deep learning that in turn will have societal impact through self-driving cars, assistive systems for the disabled, and precision medicine.

## **CONTENTS**

| AB  | STRACT                                                                                                                                                                                                                  | iii                                          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                           | ix                                           |

| LIS | ST OF TABLES                                                                                                                                                                                                            | хi                                           |

| AC  | KNOWLEDGEMENTS                                                                                                                                                                                                          | xii                                          |

| СН  | APTERS                                                                                                                                                                                                                  |                                              |

| 1.  | INTRODUCTION                                                                                                                                                                                                            | 1                                            |

|     | 1.1 Computation Requirements of Deep Learning Algorithms 1.2 Dissertation Overview 1.2.1 Thesis Statement 1.2.2 ISAAC 1.2.3 Newton 1.2.4 Evaluation of Analog Architecture for Training 1.3 Layout of This Dissertation | 1<br>3<br>4<br>4<br>5<br>5<br>5              |

| 2.  | BACKGROUND                                                                                                                                                                                                              | 7                                            |

|     | 2.1 Introduction 2.2 Computation Flow 2.3 Neural Network Layers 2.3.1 Fully-Connected layer (FC) 2.3.2 Convolution Layer 2.3.3 Pooling Layer 2.3.4 Nonlinear Layers 2.4 Conclusion                                      | 7<br>9<br>9<br>10<br>13<br>14<br>14          |

| 3.  | RELATED WORK                                                                                                                                                                                                            | 15                                           |

|     | 3.2.5.2 Quantization                                                                                                                                                                                                    | 15<br>16<br>18<br>20<br>20<br>21<br>22<br>23 |

|     | 3.2.6 Summary                                                                                                                                                                                                           | 25                                           |

|    | 3.3 Hardware Approach                                      | 25 |

|----|------------------------------------------------------------|----|

|    | 3.3.1 Digital ASICs                                        | 25 |

|    | 3.3.2 FPGA                                                 | 28 |

|    | 3.3.3 Analog Accelerator                                   | 30 |

|    | 3.4 Conclusion                                             | 31 |

| 4. | ISAAC: A CONVOLUTIONAL NEURAL NETWORK ACCELERATOR WITH     |    |

| 1. | IN-SITU ANALOG ARITHMETIC IN CROSSBARS                     | 32 |

|    | 4.1 Introduction                                           | 27 |

|    | 4.2 Background                                             |    |

|    | 4.2.1 CNNs and DNNs                                        |    |

|    | 4.2.2 Modern CNN/DNN Algorithms                            |    |

|    | 4.2.3 The DaDianNao Architecture                           |    |

|    | 4.2.4 Memristor Dot Product Engines                        |    |

|    | 4.3 Overall ISAAC Organization                             |    |

|    | 4.4 The ISAAC Pipeline                                     |    |

|    | ±                                                          |    |

|    | 4.5 Managing Bits, ADCs, and Signed Arithmetic             |    |

|    | 4.5.1 The Read/ADC Pipeline                                |    |

|    | 4.5.2 Input Voltages and DACs                              |    |

|    | 4.5.3 Synaptic Weights and ADCs                            |    |

|    | 4.5.4 Encoding to Reduce ADC Size                          |    |

|    | 4.5.5 Correctly Handling Signed Arithmetic                 |    |

|    | 4.6 Example and Intra-Tile Pipeline                        |    |

|    | 4.7 Methodology                                            |    |

|    | 4.7.1 Energy and Area Models                               |    |

|    | 4.7.2 Performance Model                                    |    |

|    | 4.7.3 Metrics                                              |    |

|    | 4.7.4 Benchmarks                                           |    |

|    | 4.8 Results                                                |    |

|    | 4.8.1 Analyzing ISAAC                                      |    |

|    | 4.8.1.1 Design Space Exploration                           |    |

|    | 4.8.2 Impact of Pipelining                                 |    |

|    | 4.8.3 Impact of Data Layout and ADCs/DACs                  |    |

|    | 4.8.4 Comparison to DaDianNao                              |    |

|    | 4.9 Conclusions                                            | 58 |

| 5. | NEWTON: GRAVITATING TOWARDS THE PHYSICAL LIMITS OF CROSSBA |    |

|    | ACCELERATION                                               | 60 |

|    | 5.1 Introduction                                           | 60 |

|    | 5.2 Background                                             |    |

|    | 5.2.1 Workloads                                            |    |

|    | 5.2.2 The Landscape of CNN Accelerators                    |    |

|    | 5.2.2.1 Digital Accelerators                               |    |

|    | 5.2.2.2 Analog Accelerators                                |    |

|    | 5.2.3 ISAAC                                                |    |

|    | 5.2.3.1 Pipeline of Memristive Crossbars                   |    |

|    | 5.2.3.2 Tiles, IMAs, Crossbars                             |    |

|    |                                                            |    |

|    | 5.2.3.3 Crossbar Challenges                              | 64  |

|----|----------------------------------------------------------|-----|

|    | 5.2.4 Crossbar Implementations                           | 64  |

|    | 5.2.4.1 Process Variation and Noise                      | 64  |

|    | 5.2.4.2 Crossbar Parasitic                               | 65  |

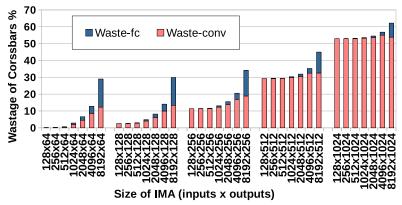

|    | 5.3 The Newton Architecture                              | 66  |

|    | 5.3.1 Intra-IMA Optimizations                            | 66  |

|    | 5.3.1.1 Mapping Constraints                              | 66  |

|    | 5.3.1.2 Bit Interleaved Crossbars                        | 66  |

|    | 5.3.1.3 An IMA as an Indivisible Resource                | 67  |

|    | 5.3.1.4 Adaptive ADCs                                    | 67  |

|    | 5.3.1.5 Divide and Conquer Multiplication                | 70  |

|    | 5.3.2 Intra-Tile Optimizations                           |     |

|    | 5.3.2.1 Reducing Buffer Sizes                            |     |

|    | 5.3.2.2 Different Tiles for Convolutions and Classifiers |     |

|    | 5.3.2.3 Strassen's Algorithm                             |     |

|    | 5.3.3 Summary                                            |     |

|    | 5.4 Methodology                                          |     |

|    | 5.4.1 Modeling Area and Energy                           |     |

|    | 5.4.2 Design Points                                      |     |

|    | 5.5 Results                                              |     |

|    | 5.5.1 Constrained Mapping for Compact HTree              |     |

|    | 5.5.2 Heterogeneous ADC Sampling                         |     |

|    | 5.5.3 Karatsuba's Algorithm                              |     |

|    | 5.5.4 eDRAM Buffer Requirements                          |     |

|    | 5.5.5 Conv-Tiles and Classifier-Tiles                    |     |

|    | 5.5.6 Strassen's Algorithm                               |     |

|    | 5.5.7 Putting it All Together                            |     |

|    | 5.6 Conclusions                                          | 87  |

| 6. | ACCELERATING TRAINING PHASE                              | 88  |

|    |                                                          |     |

|    | 6.1 Introduction                                         |     |

|    | 6.2 The Challenge of Writing to Cells                    |     |

|    | 6.3 The Challenge of Fixed Point Operations              |     |

|    | 6.4 Performance Limitations                              | 91  |

|    | 6.5 Conclusion                                           | 93  |

| 7. | CONCLUSIONS                                              | 94  |

|    | 7.1 Contribution                                         | Q/I |

|    | 7.2 Future Work                                          |     |

|    | 7.2 Puture WOIK                                          | 20  |

| DE | FED ENICES                                               | 07  |

# LIST OF FIGURES

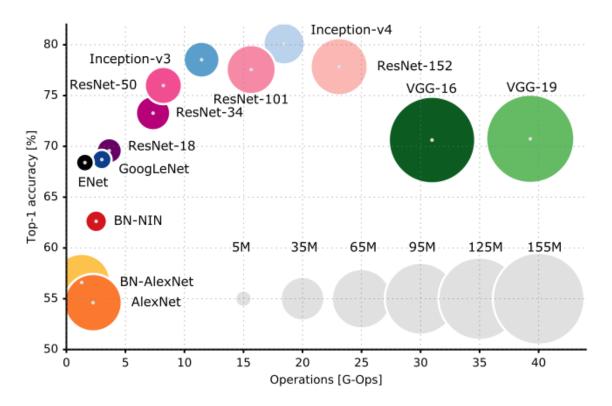

| 1.1  | The classification accuracy vs. computation requirements (GOps) for the inference step in recent well-known image classifiers [25]. The circle around each point depicts the number of parameters.                                | 3  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

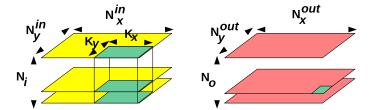

| 2.1  | The organization of a CNN layer.                                                                                                                                                                                                  | 12 |

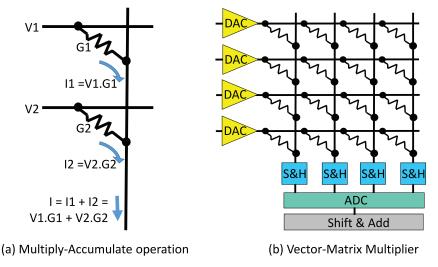

| 4.1  | Analog vector and matrix operations.(a) Using a bitline to perform an analog sum of products operation. (b) A memristor crossbar used as a vector-matrix multiplier.                                                              | 38 |

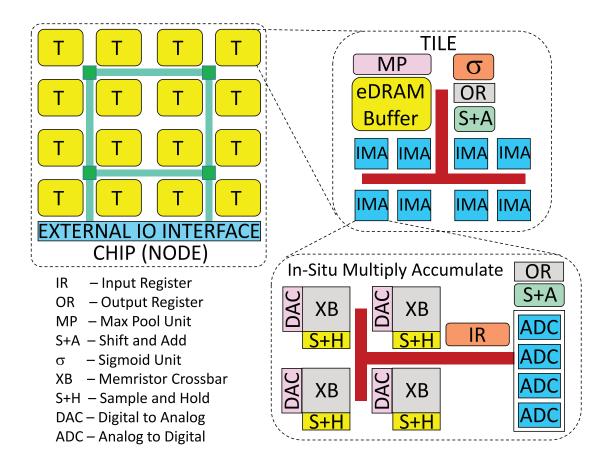

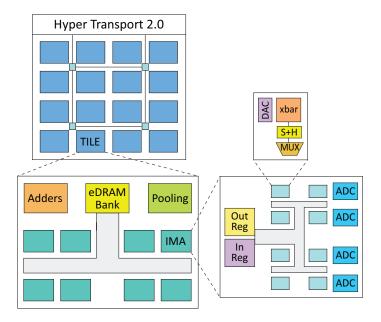

| 4.2  | ISAAC architecture hierarchy                                                                                                                                                                                                      | 39 |

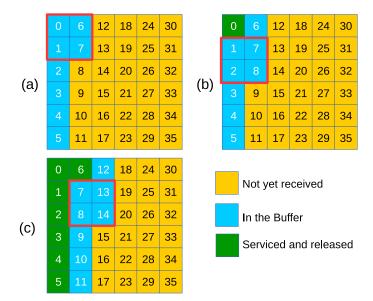

| 4.3  | Minimum input buffer requirement for a $6 \times 6$ input feature map with a $2 \times 2$ kernel and stride of 1. The blue values in (a), (b), and (c) represent the buffer contents for output neurons 0, 1, and 7, respectively | 41 |

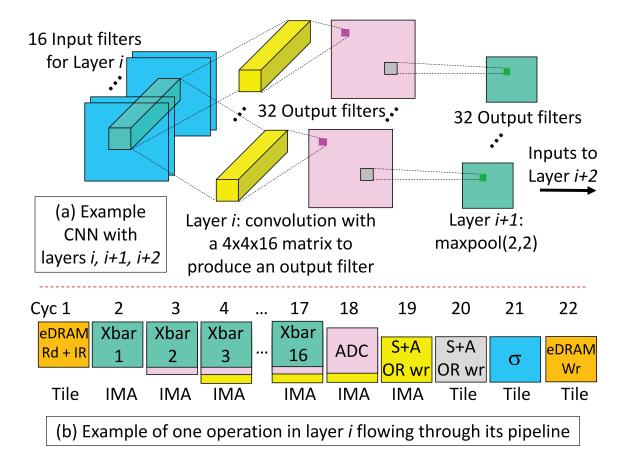

| 4.4  | Example CNN layer traversing the ISAAC pipeline                                                                                                                                                                                   | 48 |

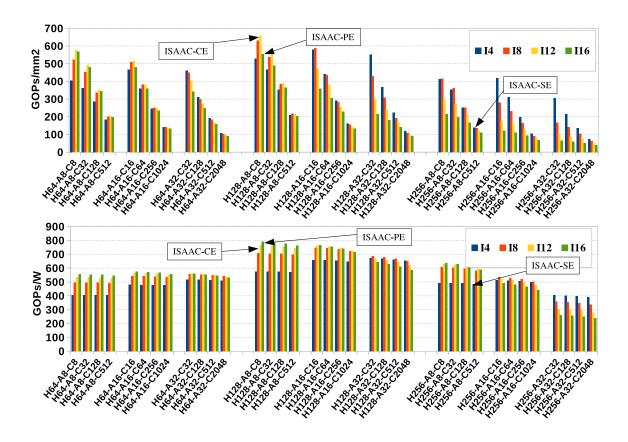

| 4.5  | CE and PE numbers for different ISAAC configurations. H128-A16-C4 for bar I8 corresponds to a tile with 8 IMAs, 16 ADCs per IMA, and 4 crossbar arrays of size 128×128 per IMA                                                    | 54 |

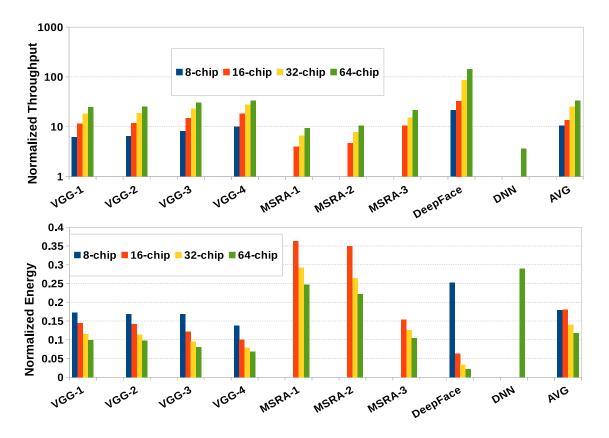

| 4.6  | Normalized throughput (top) and normalized energy (bottom) of ISAAC with respect to DaDianNao                                                                                                                                     | 59 |

| 5.1  | The ISAAC Architecture                                                                                                                                                                                                            | 64 |

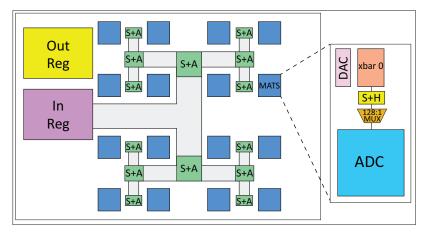

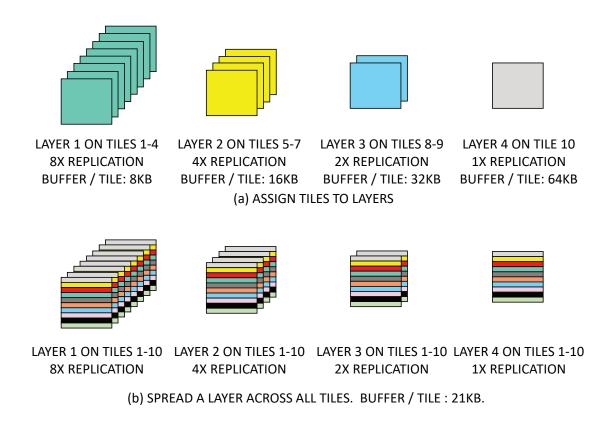

| 5.2  | Microarchitecture of an IMA                                                                                                                                                                                                       | 67 |

| 5.3  | Heterogeneous ADC sampling resolution                                                                                                                                                                                             | 68 |

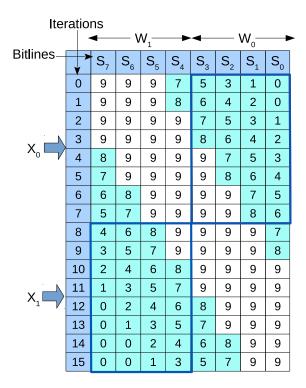

| 5.4  | Karatsuba's Divide & Conquer Algorithm                                                                                                                                                                                            | 70 |

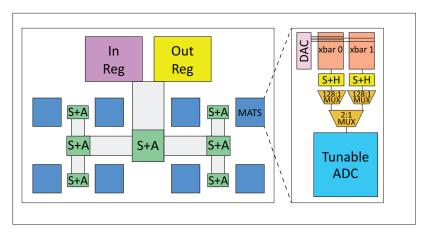

| 5.5  | IMA supporting Karatsuba's Algorithm                                                                                                                                                                                              | 71 |

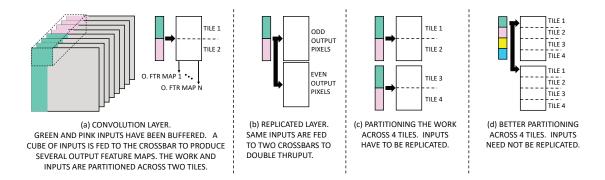

| 5.6  | Mapping of convolutional layers to tiles                                                                                                                                                                                          | 73 |

| 5.7  | Mapping layers to tiles for small buffer sizes                                                                                                                                                                                    | 74 |

| 5.8  | Strassen's Divide & Conquer Algorithm for Matrix Multiplication                                                                                                                                                                   | 76 |

| 5.9  | Mapping Strassen's algorithm to a tile                                                                                                                                                                                            | 76 |

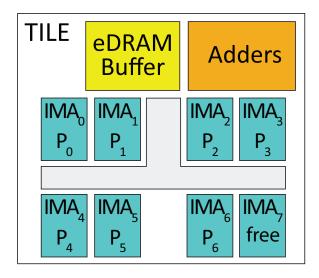

| 5.10 | Crossbar under-utilization with constrained mapping                                                                                                                                                                               | 81 |

| 5.11 | Impact of constrained mapping and compact HTree                                                                                                                                                                                   | 81 |

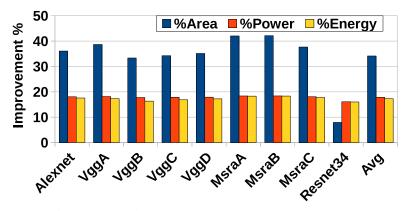

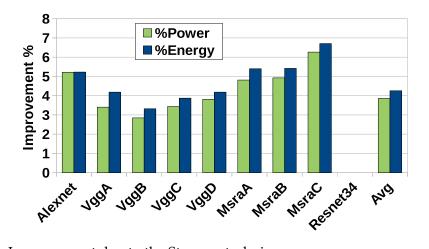

| 5.12 | Improvement due to the adaptive ADC scheme                                                                                                                                                                                        | 82 |

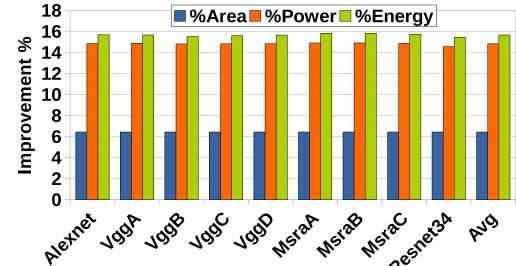

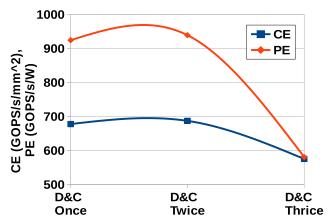

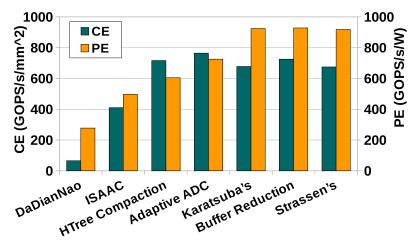

| 5.13 | Comparison of CE and PE for Divide and Conquer done recursively                                                                                                                                                                   | 82 |

| 5.14 | Improvement with Karatsuba's Algorithm                                                                                                                                                                                            | 82 |

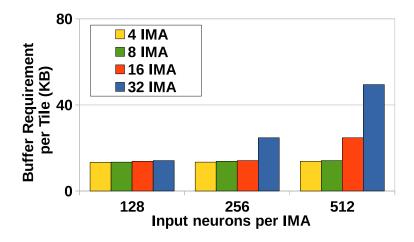

| 5.15 | number of IMAs                                                                                  | 84 |

|------|-------------------------------------------------------------------------------------------------|----|

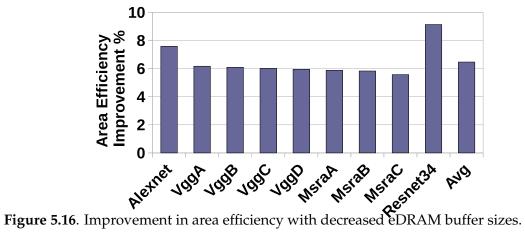

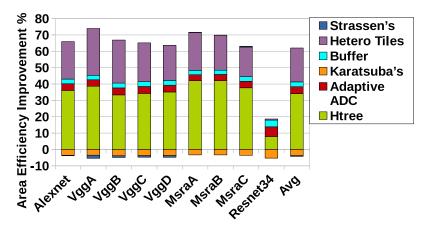

| 5.16 | Improvement in area efficiency with decreased eDRAM buffer sizes                                | 84 |

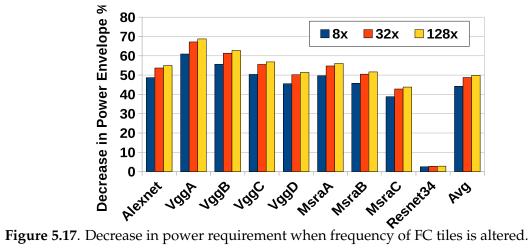

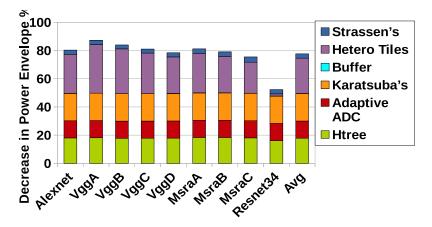

| 5.17 | Decrease in power requirement when frequency of FC tiles is altered                             | 84 |

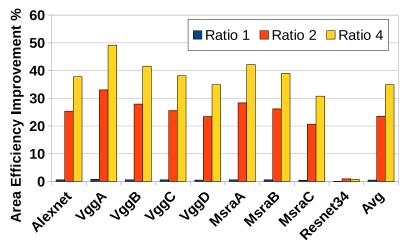

| 5.18 | Improvement in area efficiency when sharing multiple crossbars per ADC in FC tiles.             | 85 |

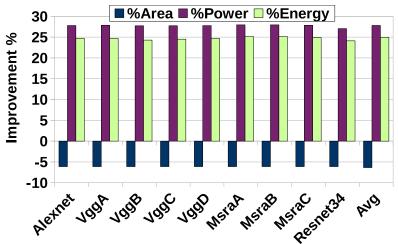

| 5.19 | Improvement due to the Strassen technique                                                       | 85 |

| 5.20 | Peak CE and PE metrics of different schemes along with baseline digital and analog accelerator. | 86 |

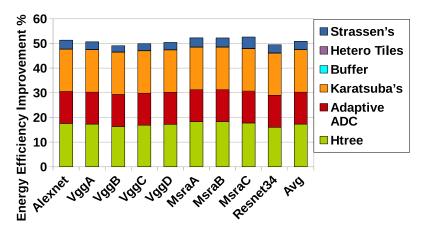

| 5.21 | Breakdown of area efficiency                                                                    | 86 |

| 5.22 | Breakdown of decrease in power envelope                                                         | 87 |

| 5.23 | Breakdown of energy efficiency                                                                  | 87 |

# LIST OF TABLES

| 4.1 | ISAAC Parameters                                                                                                                                                                                                                | 50 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Benchmark names are in bold. Layers are formatted as $K_x \times K_y$ , $N_o$ /stride (t), where t is the number of such layers. Stride is 1 unless explicitly mentioned. Layer* denotes convolution layer with private kernels | 53 |

| 4.3 | Buffering requirement with and without pipelining for the largest layers                                                                                                                                                        | 55 |

| 4.4 | Comparison of ISAAC and DaDianNao in terms of CE, PE, and SE. Hyper-Transport overhead is included                                                                                                                              | 58 |

| 5.1 | Key contributing elements in Newton.                                                                                                                                                                                            | 78 |

| 5.2 | Benchmark names are in bold. Layers are formatted as $K_x \times K_y$ , $N_o$ /stride (t), where t is the number of such layers. Stride is 1 unless explicitly mentioned                                                        | 79 |

|     |                                                                                                                                                                                                                                 |    |

### **ACKNOWLEDGEMENTS**

Before coming to the U.S. for my Ph.D., I lived all my life in Tehran, close to my family. My parents selflessly encouraged me to leave for greater achievements, while they badly want me to be there. Having them is one of the greatest blessings in my life. Their love and support are far beyond what words can describe.

I was honored and privileged to have Rajeev Balasubramonian as my Ph.D. Advisor. Not only did he teach me how to research, but he also taught me how to live and prosper. I really appreciate his patience and support. <sup>1</sup>

I would like to thank my Ph.D. committee, Al Davis, Erik Brunvand, Mahdi Bojnordi, and Vivek Srikumar, for their feedback and support during my Ph.D. Moreover, I learned life lessons from Al, critical thinking from Erik in the reading club, the basics of machine learning from Vivek's course, and the inspiration to always keep the bar high from Mahdi.

I would like to thank my mentor, Naveen Muralimanohar of Hewlett Packard Enterprise, who trusted me with doing research on in-situ computing, and other people at HPE Lab that generously shared their invaluable knowledge with me.

To me, the main goal of the Ph.D. was to make great friends. This way, I can certainly call my Ph.D. a success. When I came to Salt Lake City in 2012, I did not know anyone. Five years later, I had many life-lasting friends. I would like to thank them all. I enjoyed the time I spent with Uarch members, Ani, Kshitij, Nil, Seth, Manju, Sahil, Akhila, Arjun, Chandru, Surya, and Karl. I would like to especially thank Anirban, Meysam, and Peyman, who helped me with my dissertation. I would like to thank many other friends, with whom I shared a lot of great moments. <sup>2</sup> I am blessed with their friendship.

I would like to thank Karen, Ann, Robert, Leslie, Chethika, and other amazing people at the University of Utah for their enormous support.

<sup>&</sup>lt;sup>1</sup>and the ping-pong table.

<sup>&</sup>lt;sup>2</sup>especially the surprise birthday celebration near the ISCA deadlines.

Although I specifically thanked a few people, I am fully aware and appreciate many others who indirectly encouraged me, inspired me, or made this journey much easier for me.

### CHAPTER 1

### INTRODUCTION

### 1.1 Computation Requirements of Deep Learning Algorithms

The field of Machine Learning helps develop computation models that learn the environment without explicit programming. The goal is to reach human intelligence and beyond.

To this end, researchers have developed many models such as SVM (support vector machine), decision trees, and regression.

One of the most promising models so far is artificial neural networks (ANNs). Inspired by biological neurons, McCulloch and Pitts developed the first model of ANNs in 1943. Later, at the end of the 1950s, a *perceptron* had been proposed, raising optimism about imminent human level intelligence [155]. However, in 1969, Minsky and Papert showed the weaknesses of the perceptron model, which discouraged further activity in ANNs [128]. In the 70s and 80s, backpropagation had been introduced and developed for training a neural network from raw data. Later in the 90s, LeCun et al. proposed convolutional neural networks (CNNs) leading to promising results in handwritten character recognition [103].

Even with the advent of CNNs, researchers were still relying on other approaches such as SVM or ensemble of different models to achieve the best results.

The power of ANNs was revealed to researchers as the size of networks and training data sets grew. Particularly, Alexnet was a milestone that won the ImageNet competition in 2012 [96] by reducing the error rate by almost a factor of two, compared to other approaches. This work successfully trained a multimillion-parameter network with millions of raw input images using back-propagations. Alexnet training took 6 days. Without a high-speed GPU for training, Alexnet training would have taken much longer. In other words, the computation power of today's machines is a primary driver for major advancements in the field of machine learning. Machine learning researchers have also developed

a number of techniques in the last decade to help deep networks learn, e.g., the use of shared weights, dropout, expanded inputs, better activation functions, and regularization.

The Alexnet structure – a sequence of convolutional layers followed by fully-connected classifier layers that is used for image classification – has also been used in many subsequent works and rejuvenated the field of *deep learning*. In deep learning, multiple nonlinear layers automatically extract and abstract features from raw data for different purposes such as classification and prediction. The deeper layers in the networks combine more simple features from the earlier layers to extract more complex features and recognize complicated objects in input images. Such deep neural networks (DNNs) have recently achieved better results than human image classification. However, these outstanding results are not for free; DNNs require billions of operations per image for the simple task of classification. Figure 1.1 shows the top-1 accuracy and the computational requirements for recent DNNs. In this figure, the trend suggests that more computation leads to higher accuracy. In addition, the computational requirement grows significantly with increase in the size of input, number of training samples, and the number of classification categories. Therefore, providing faster machines is essential.

Deep networks have to be trained. The training currently takes many weeks across several high-powered GPUs in a datacenter. Once the network is trained, it is deployed on several devices (datacenter servers, self-driving cars, drones, mobile devices, etc.), where it performs *inference* on billions of images every day. Faster machines are not only essential for the training operations in deep networks, they are also essential for inference operations. This dissertation focuses on both inference and training.

One promising solution to the computational requirements of DNNs is hardware specialization. It is well known that custom ASICs can be up to three orders of magnitude faster than general purpose systems [69].

Since effective neural networks have always been computation-intensive, there have been many prototypes and hardware architecture proposals.

Most of this prior work focuses on digital architectures, and we review some of them in the background chapter. In this dissertation, we explore the use of analog units for DNN acceleration and make some of the first contributions in the field of in-situ analog computing for DNNs.

**Figure 1.1**. The classification accuracy vs. computation requirements (GOps) for the inference step in recent well-known image classifiers [25]. The circle around each point depicts the number of parameters.

To make the potential impact of this work clear, consider the following concrete use case. Some modern cars (and likely most cars in the future) use a variety of cameras and sensors to gather road/traffic information. Processing this information will require computers that consume several hundreds of watts and precious space. The accelerators defined in this dissertation will help process many more images (safety) with a computing system that consumes tens of watts (energy efficiency) and fits under the seat of the car.

### 1.2 Dissertation Overview

Machine learning algorithms are a good candidate for specialization as they are embarrassingly parallel and require massive computation power. Most of the execution time of these algorithms is spent on computing convolution and classifier layers. All of these layers can be expressed as matrix-by-vector multiplications followed by a nonlinear activation. Machine learning algorithms also require a large set of parameters; much of the

time and power spent on these algorithms can be attributed to the high cost of moving these parameters between memory and computational units.

#### 1.2.1 Thesis Statement

We hypothesize that analog units have the potential to dramatically improve efficiency for inference in machine learning accelerators because of their ability to perform in-situ calculations and reduce data movement. We further hypothesize that clever management of the ADC units will be vital in realizing the potential of in-situ computation.

#### 1.2.2 **ISAAC**

A number of recent efforts have attempted to design accelerators for popular machine learning algorithms, such as those involving convolutional and deep neural networks (CNNs and DNNs). These algorithms typically involve a large number of multiply-accumulate (dot-product) operations. A recent project, DaDianNao, adopts a near data processing approach, where a specialized neural functional unit performs all the digital arithmetic operations and receives input weights from adjacent eDRAM banks.

Chapter 4 explores an in-situ processing approach, where memristor crossbar arrays not only store deep network parameters (the synaptic weights), but are also used to perform dot-product operations in an analog manner. No prior work has designed or characterized a full-fledged DNN accelerator based on crossbars. In particular, our work makes the following contributions: (i) We design a pipelined tiled architecture, with some crossbars dedicated for each neural network layer, and eDRAM buffers that aggregate data between pipeline stages. (ii) We define new data encoding techniques that are amenable to analog computations and that can reduce the high overheads of analog-to-digital conversion (ADC). (iii) We define the many supporting digital components required in an analog CNN accelerator and carry out a design space exploration to identify the best balance of memristor storage/compute, ADCs, and eDRAM storage on a chip. On a suite of CNN and DNN workloads, the proposed ISAAC architecture yields improvements of 14.8×, 5.5×, and 7.5× in throughput, energy, and computational density (respectively), relative to the state-of-the-art DaDianNao architecture.

#### **1.2.3** Newton

Using ISAAC as a starting point, we then create a next-generation architecture, Newton, described in Chapter 5 of the dissertation. Newton addresses two significant short-comings in ISAAC. First, ISAAC is a homogeneous design where every resource is provisioned for the worst case. Second, the ADCs account for a large fraction of chip power and area. By addressing both problems, Newton moves closer to achieving optimal energy-per-neuron for crossbar accelerators.

We introduce six new techniques that apply at different levels of the tile hierarchy. Two of the techniques leverage heterogeneity: one adapts ADC precision based on the requirements of every subcomputation (with zero impact on accuracy), and the other designs tiles customized for convolutions or classifiers. Two other techniques rely on divide-and-conquer numeric algorithms to reduce computations and ADC pressure. The final two techniques place constraints on how a workload is mapped to tiles, thus helping reduce resource provisioning in tiles. For a wide range of CNN dataflows and structures, Newton achieves a 77% decrease in power, 51% improvement in energy efficiency, and  $2.2 \times higher throughput/area$ , relative to ISAAC accelerator.

### 1.2.4 Evaluation of Analog Architecture for Training

We also evaluate the potential of using an analog accelerator for training DNNs. We show that due to three major weaknesses, analog accelerators are not as efficient as digital ones for training. First, analog accelerator endurance is limited because today's large data sets cause millions of weight updates per training iteration. Second, analog accelerators work with fixed point operators, which reduces the operation accuracy and consequently increases the trained networks' error rate. Finally, analog accelerators can only expedite the forward and backward paths, but they require far more time for weight updates.

### 1.3 Layout of This Dissertation

The rest of this dissertation is organized as follows. In Chapter 2, we explain the computation requirement of DNNs in both inference and training phases. In Chapter 3, we review the prior software and hardware-related work to accelerate DNNs. Chapter 4 and Chapter 5 cover proposed architectures, ISAAC and Newton, respectively. We investigate

in-situ computing to accelerate DNN training in Chapter 6. Finally, Chapter 7 discusses our primary conclusions.

### CHAPTER 2

### **BACKGROUND**

### 2.1 Introduction

In this chapter we explain the computational requirements of deep neural networks (DNNs). DNNs are built by connecting different layers of neurons serially or in parallel, and they typically represent a direct acyclic graph (DAG) of computations. Depending on the applications, one might leverage different types of layers. In this section, we review some of the common layers, in both inference (forward path) and training phase (backward error propagation). More specifically, we review both forward and backward paths for fully-connected, convolution, pooling, sigmoid, and ReLU layers.

### 2.2 Computation Flow

Since DNNs are DAGs, the flow of computation in the inference mode is straightforward. The input data is the first layer's input and the output of each layer will serve as the input for the next layer in the graph of computation. In the case of classification, the last layer's neurons can be interpreted as the predicted chance of one classes.

In the training mode, a pair of sample data and a label will be considered as the input. Similar to the inference mode, DNN receives the sample data and generates a vector of probability as its output. Then a loss function (also known as cost function) evaluates the result by comparing it with the label. The goal of training is to reduce the loss function. One can consider the entire neural network as one complex function. The goal is to reduce the sum of the loss function output for all the training samples. Assume  $S = \{(x_i, l_i) | i \in \{0, ..., N-1\} \}$  is the set of training samples with N members. Also consider a neural network with M cascaded layers. We represent Layer i with a function  $f_i(x)$  and its parameters as  $W^{(i)}$ . Therefore, the output of the entire network, for the input  $x_i$  is

$$out_i = f_{M-1}(...(f_2(f_1(x_i)))...)$$

(2.1)

The loss value for this input is  $Loss(out_i, l_i)$ . The goal is to minimize the following equation.

$$L = \sum_{i=0}^{N-1} Loss(out_i, l_i)$$

(2.2)

There are multiple ways to solve this optimization problem. In the *gradient descent* approach, in each step, L is calculated and  $W^{(i)}$  are updated in a direction to get closer to the local minimum. For the layer k, the i-th parameter is updated using the following rule:

$$W_i^{(k)} = W_i^{(k)} - \eta \times \frac{\partial L}{\partial W_i^{(k)}}$$

(2.3)

In the above equation,  $\eta$  is the *learning rate*. Large  $\eta$  values lead to fast convergence at the risk of missing some local minimum. On the other hand, small  $\eta$ s do not jump over optimum points at the cost of slower convergence.

The problem with gradient descent is that for every update step, we have to calculate all  $out_i$ s. Therefore, the time for each step grows linearly with the training set size. As a result, this technique is not used for large-scale DNNs in practice. Instead, *stochastic gradient descent* will be applied. In this approach, the training set is shuffled and decomposed into many small *minibatches* and gradient descent is applied to each minibatch. Therefore, the number of outputs involved in each parameter update step is a function of the number of elements in each minibatch. In practice, minibatches are much smaller than the training set. The process of training all the minibatches is called an *epoch*. Since updating parameters is based on a few samples in the minibatch, the training is carried for multiple epochs.

In each weight update step, we also need to calculate the gradient of each weight with respect to the loss function. Applying the chain rule, we can find the gradient for the functional representation of the neural networks (Eq. 2.1).

$$\frac{\partial L}{\partial W_{i}^{(k)}} = \frac{\partial L}{\partial y_{N-1}} \times \frac{\partial y_{N-1}}{\partial W_{i}^{(k)}}$$

$$\frac{\partial y_{M-1}}{\partial W_{i}^{(k)}} = \frac{\partial y_{M-1}}{\partial y_{M-2}} \times \frac{\partial y_{M-2}}{\partial W_{i}^{(k)}}$$

...

$$\frac{\partial y_{k+1}}{\partial W_{i}^{(k)}} = \frac{\partial y_{k+1}}{\partial y_{k}} \times \frac{\partial y_{k}}{\partial W_{i}^{(k)}}$$

(2.4)

In Eq. 2.4,  $y_r$  is the output of r-th layer ( $out_i = y_{N-1}$ ). This process is called backward error propagation or backpropagation, where the loss error  $\frac{\partial L}{\partial y_{N-1}}$  is propagated in the opposite direction of inference networks. In the backward network, the intermediate results of layer t is  $e_t = \frac{\partial L}{\partial y_{M-1-t}}$  and the parameters in the backward network are  $\frac{\partial y_t}{\partial y_{t-1}}$ . We have,

$$\frac{\partial L}{\partial y_t} = \frac{\partial y_t}{\partial y_{t-1}} \times \frac{\partial L}{\partial y_{t-1}}$$

$$e_t = \frac{\partial y_t}{\partial y_{t-1}} \times e_{t-1}$$

(2.5)

Therefore, one can rewrite gradient calculation in Eq. 2.4 as follows.

$$e_{0} = \frac{\partial L}{\partial y_{M-1}}$$

$$e_{1} = \frac{\partial y_{M-1}}{\partial y_{M-2}} \times e_{0}$$

$$\cdots$$

$$e_{k} = \frac{\partial y_{k-1}}{\partial y_{k-2}} \times e_{k-1}$$

$$\frac{\partial L}{\partial W_{i}^{(k)}} = e_{k} \times \frac{\partial y_{k}}{\partial W_{i}^{(k)}}$$

$$(2.6)$$

$\frac{\partial y_k}{\partial W_i^{(k)}}$  depends on the input of Layer k (i.e.,  $y_{k-1}$ ). In other words, in the process of weight update both  $y_i$ s and  $e_i$ s are needed.

In the following part of this chapter we discuss the functionality of some of the most popular layers.

### 2.3 Neural Network Layers

In this section we review some of the most popular layers deployed in deep learning architecture.

### 2.3.1 Fully-Connected layer (FC)

This is the most used layer in the history of neural networks. In this layer, every output neuron is the weighted sum of every input neuron (Eq. 2.7). The layer is illustrated as a bipartite graph with one side representing input neurons while the other sides are output neurons. In between any pair of input neuron,  $N_i$ , and output neuron,  $M_j$ , there is an edge labeled with the weight  $w_{i,j}$ . This layer can also be represented as a matrix by vector

multiplication  $W \times N = M$ , where W, N, and M are the weight matrix, the vector of input neuron values, and the vector of output neuron values, respectively. we have

$$M_j = \sum_{i=0}^{n-1} W_{i,j} \times N_i \tag{2.7}$$

where n is the number of element input neurons. Similarly, we define m as the number of output neurons. With the above notation, we can now derive the backpropagation rules for FC layer.

$$\frac{L}{\partial N_i} = \sum_{j=0}^{m-1} \frac{\partial L}{\partial M_j} \times \frac{\partial M_j}{\partial N_i}

\frac{L}{\partial N_i} = \sum_{j=0}^{m-1} \frac{\partial L}{\partial M_j} \times W_{i,j}$$

(2.8)

if  $e_{in} = \left[\frac{L}{\partial N_i}\right]_{0 \le i < n}$  and  $e_{out} = \left[\frac{L}{\partial M_i}\right]_{0 \le i < m}$  are the input and output error vectors, we can write:

$$e_{in} = W^T \times e_{out} \tag{2.9}$$

where T is the matrix transpose operation. In addition to the error propagation, we have to calculate the gradient of each weight with respect to the output layer.

$$\frac{\partial L}{\partial W_{i,j}} = \sum_{t=0}^{m-1} \frac{\partial L}{\partial M_t} \times \frac{\partial M_t}{\partial W_{i,j}}$$

$$\frac{\partial L}{\partial W_{i,j}} = \frac{\partial L}{\partial M_j} \times \frac{\partial M_j}{\partial W_{i,j}}$$

$$\frac{\partial L}{\partial W_{i,j}} = \frac{\partial L}{\partial M_i} \times N_i$$

(2.10)

As shown in Eq. 2.10, the gradient for the FC layer depends on the inputs and the propagated error in the output.

FC layers requires  $m \times n$  parameters,  $m \times n$  multiplications and  $m \times n$  additions.

### 2.3.2 Convolution Layer

In the FC layer, all input neurons have influence on all the output neurons, which causes two problems: (i) the FC layer cannot preserve features that depend on the spatial locality and (ii) the number of parameters and operations increase superlinearly.

Convolution Layer has been proposed to address these two weaknesses. In a convolution layer, input and output neurons are organized in an array of *channels*, each of which are 2D arrays of input neurons. By this organization, the input and output are considered as 3D arrays. <sup>1</sup> For example, in image classification, input image to the neural network is considered as 3 channels of images, one for red color, one blue color, and one for green color. In general, we assume the input has  $N_i$  input channels of  $N_x^{in} \times N_y^{in}$  and the outputs consists of  $N_o$  output channels of  $N_x^{out} \times N_y^{out}$ . In our notation, we call input channel i and output channel j as  $ch_i^{in}$  and  $ch_j^{out}$ , respectively.

The parameters are organized as 4D arrays: an  $Ni \times N_o$  arrays of *kernels*  $K_{i,j}$ , where each kernel is a  $Ky \times K_y$  array of weights. Figure 2.1 depicts the general convolution layer organization.

Using the above notation, one can write the convolution layer function as follows.

$$ch_{j}^{out} = \sum_{r=0}^{N_{in}-1} ch_{r}^{in} \otimes K_{r,j}$$

(2.11)

In Eq. 2.11, the summation on channels is element-wise summation.

The operation  $\otimes$  is 2D convolution operation with two 2D arrays and generates one 2D array outputs. In general, 2D convolution is performed using the following equation.

$$B = A \otimes K$$

$$B[i][j] = \sum_{t=0}^{K_y - 1} \sum_{r=0}^{K_x - 1} A[i \times s_x + r][j \times s_y + t] \times K[r][s]$$

$$for \ s_x = s_y = 1 \Rightarrow B[i][j] = \sum_{t=0}^{K_y - 1} \sum_{r=0}^{K_x - 1} A[i + r][j + t] \times K[r][s]$$

(2.12)

One can describe this operation as the kernel K rolling over 2D array A in multiple steps. In each step, one output entry is calculated by performing inner product of K with the part of A covered by K. In Eq. 2.12,  $s_x$  and  $s_y$  are the strides in x and y dimensions.

Notice that a convolution layer is the general case of the FC layer, where input neurons are replaced with 2D channels, weights are replaced with 2D kernels, and the product of an input and a weight are replaced with 2D convolution operation. If channel and kernels are  $1 \times 1$ , we end up with an FC layer.

One advantage of this interpretation is that we can leverage the FC equations for backpropagation. However, we still need to understand how 2D convolution operations impact error propagation. To this end, we first looked into a case where we have one input

<sup>&</sup>lt;sup>1</sup>Input and output will be 4D arrays if a batch of sample data is considered.

Figure 2.1. The organization of a CNN layer.

$A_{n_1 \times n_2}$  and output channels  $B_{m_1 \times m_2}$  with kernel  $K_{x \times y}$ . If we know the impact of error propagation in this case, we can extend it to convolution layers with more input and/or output channels, with the help of equations developed for the FC layer.

Assuming  $s_x = s_y = 1$ , we have:

$$\frac{\partial L}{\partial A[m][n]} = \sum_{r} \sum_{t} \frac{\partial L}{\partial B[r][t]} \times \frac{\partial B[r][t]}{\partial A[m][n]}$$

$$\frac{\partial L}{\partial A[m][n]} = \sum_{i=0}^{x-1} \sum_{j=0}^{y-1} \frac{\partial L}{\partial B[m-i][n-j]} \times \frac{\partial B[m-i][n-j]}{\partial A[m][n]}$$

$$\frac{\partial L}{\partial A[m][n]} = \sum_{i=0}^{x-1} \sum_{j=0}^{y-1} \frac{\partial L}{\partial B[m-i][n-j]} \times K[i][j]$$

(2.13)

If  $e_A = \left[\frac{\partial L}{\partial A[i][j]}\right]$  and  $e_B = \left[\frac{\partial L}{\partial B[i][j]}\right]$  are the error maps for the input and output channel, then one can write:

$$\frac{\partial L}{\partial A[m][n]} = \sum_{i=0}^{x-1} \sum_{j=0}^{y-1} \frac{\partial L}{\partial B[m-i][n-j]} \times K[i][j]$$

$$e_A[m][n] = \sum_{i=0}^{x-1} \sum_{j=0}^{y-1} e_B[m-i][n-j] \times K[i][j]$$

$$define \ m' = (m-x+1) \ and \ n' = (n-y+1)$$

$$e_A[m][n] = \sum_{i=0}^{x-1} \sum_{j=0}^{y-1} e_B[m'+(x-1-i)][n'+(y-1-j)] \times K[i][j]$$

$$define \ i' = (x-1-i) \ and \ j' = (y-1-j)$$

$$e_A[m][n] = \sum_{i'=0}^{x-1} \sum_{j'=0}^{y-1} e_B[m'+i'][n'+j'] \times K[x-1-i'][y-1-j']$$

By changing the variables we can rewrite the equation as:

$$e_{B}^{pad}[m][n] = e[m-x+1][n-y+1] = e[m'] \text{ if } m \geq x-1 \text{ } n \geq y-1$$

$$otherwise \implies e_{B}^{pad}[m][n] = 0$$

$$Also \text{ } define \text{ } K'[i][j] = [x-1-i][y-1-j]$$

$$e_{A}[m][n] = \sum_{i'=0}^{x-1} \sum_{j'=0}^{y-1} e_{B}[m'+i'][n'+j'] \times K[x-1-i'][y-1-j']$$

$$e_{A}[m][n] = \sum_{i=0}^{x-1} \sum_{j=0}^{y-1} e_{B}^{pad}[m+i][n+j] \times K'[i][j]$$

$$e_{A} = e_{B}^{pad} \otimes K'$$

In other words, error map in the input channel is the convolution of output channel error maps that has been padded with zeros (i.e.,  $e_B^{pad}$ ) with the rotated version of the original kernel (i.e., K').

In general for  $N_i$  input channels and  $N_o$  output channels, we have:

$$e_{ch_{i}^{in}} = \sum_{j=0}^{N_{o}-1} e_{ch_{i}^{out}}^{pad} \otimes K'_{i,j}$$

(2.16)

Similarly, the weight update array for kernel  $K_{i,j}$  is calculated as follows:

$$\frac{\partial L}{\partial K_{i,j}} = e_{ch_j^{out}}^{pad} \otimes ch_i^{in}$$

(2.17)

In general, we can state that both forward and backward operations are convolutional operations. The number of parameters in this layer is  $N_o \times N_i \times K_x \times K_y$  and the number of operations for additions and multiplications  $N_o \times N_x^{out} \times N_y^{out} \times (N_i \times K_x \times K_y)$ .

### 2.3.3 Pooling Layer

As we mentioned, the number of operations in the convolution layer depends on the size of channels. A pooling layer is proposed to down-sample output channels of the convolution layers. A pooling layer is applied per channel. Therefore, it preserves the number of channels in the input. However, the output channels have smaller dimensions. There are two common types of pooling layers, average pooling and max pooling. Average pooling is a 2D convolution operation of Kernel  $K_{K_x \times K_y}$  with all its weights equal to  $\frac{1}{K_x \times K_y}$ . Max pooling, on the other hand, is a 2D convolution with Kernel  $1_{K_x \times K_y}$  that uses max operation instead of addition. It is also worth noting that the strides in pooling layers are typically greater than one to reduce the dimensions of the resulting output channels.

Since the average pooling is essentially 2D convolution, we can apply Eq. 2.15 to calculate its error maps. For max pooling, error in the output is just propagated to the input with the maximum values.

When a pooling layer with kernel of size  $K_x \times K_y$  kernel and strides of size  $s_x$  and  $s_y$  is applied to  $N_i$  input channels of size  $N_x \times N_y$ ,  $\frac{N_x \times N_y \times K_x \times K_y}{s_x \times s_y}$  operations are required.

### 2.3.4 Nonlinear Layers

The secret ingredient in DNNs is nonlinearity. Without nonlinear layers, DNNs are simply a polynomial function of input values. There are three types of nonlinear layers; sigmoid, tanh, and ReLU. These functions are represented by the following equations:

$$\sigma(x) = \frac{1}{1 + e^{-x}}$$

$$\tanh(x) = 2\sigma(2x) - 1$$

$$ReLU(x) = \max(0, x)$$

(2.18)

Many recent DNNs have adopted ReLU due to its simplicity and high accuracy. However, sigmoid and tanh are still used in LSTMs (Long Short Term Memory). Additionally, some work suggests to approximate the exponential operator in sigmoid and tanh with piece-wise linear functions [28].

Although sigmoid and tanh have exponential operators, they are simply differentiable based on the forward path values.

$$\frac{\partial \sigma(x)}{\partial x} = \sigma(x)(1 - \sigma(x))$$

$$\frac{\partial tanh(x)}{\partial x} = (1 + tanh(x)) \times (1 - tanh(x))$$

$$\frac{\partial ReLU(x)}{\partial x} = \begin{cases} 1 & \text{if } x \ge 0\\ 0 & \text{if } x < 0 \end{cases}$$

(2.19)

### 2.4 Conclusion

In this section, we reviewed common layers used in state-of-the-art DNNs. We showed that computation intensive layers such as convolutions and FC have the same type of operations in both forward and backward paths.

### **CHAPTER 3**

### **RELATED WORK**

### 3.1 Introduction

In this chapter, we review some of the previous work that aims to simplify DNN programmability or acceleration. We first review software solutions for CPUs and GPUs on datacenters or mobile platforms (Section 3.2). Then, we review both analog and digital hardware implementations of DNNs (Section 3.3). Finally, we conclude this chapter in Section 3.4.

### 3.2 Software Approach

There are multiple software approaches to accelerate DNNs. In this section, we categorize them into four groups. In the first two subsections, we review software solutions for CPU-based and GPU-based platforms. Then we list some of the popular Deep Learning frameworks that simplify DL programming. Some of these frameworks are also able to distribute DNNs over multiple machines. Finally, we look into approximation approaches that aim to reduce the number of operations without a loss in accuracy.

### 3.2.1 Software Optimization for CPUs

Matrix-by-vector multiplication, or MVM, is the key operation in DNNs. Therefore, it is possible to take advantage of efficient linear algebra libraries to accelerate these algorithms. The de-facto standard for linear algebra is BLAS (Basic Linear Algebra Subprogram), which is a set of function specifications commonly used in linear algebra. Libraries such as OpenBlas [142], ATLAS [15], Intels MKL [130] are the implementations of the BLAS interface. ATLAS (Automatically Tuned Linear Algebra Software) is a library that tunes its parameters based on the host hardware. MKL (Math Kernel Library) takes advantage of Intel AVX (Advanced Vector Extension) instructions and Intel SSE2 code to optimize operations such linear algebra, FFT (Fast Fourier Transform), statistics, and PDEs (Partial

Differential Equations).

Besides BLAS, Eigen [53], a C++ template library, l is also used for linear algebra operations. This library is designed to be versatile, fast, and reliable. Depending on the host, it tries to take advantage of available vector instructions (e.g., Intel AVX, ARM NEON, and PowerPC AltiVec).

Other libraries such as Blaze [21], Armadillo [161], UBLAS [2] by Boost, and (Matrix Template Library) MTL [185] are also used for linear algebra. However, they are not that popular among DL frameworks compared with others mentioned earlier.

In addition to dense Linear Algebra, some DNNs rely on sparse MVMs; popular sparse libraries for CPUs are Intel MKL and ViennaCL. Augusto et al. compare these algorithms, in terms of performance, and report the superiority of Intel MKL in terms of performance [16].

There have been some comparisons between different techniques and code optimizations for DNNs on CPUs. Vanhoucke et al. use a speech recognition algorithm and show that memory layout, batching and clever usage of SSE2 and taking advantages of fixed-point instructions in SSE3 can improve performance by 10x [186]. Cong and Xia propose optimized matrix multiplication operations to reduce the number of CPU operation by up to 47% [40].

Rajbhandari et al. characterized the GEMM (General Matrix Multiply) operations (i.e., GEMM-in-Parallel and Parallel-GEMM) for CNN on CPU and proposed an optimization framework that generates optimized sparse codes as well as a scheduler based on GEMM-in-Parallel citerajbhandarihe17.

Besides the works focusing on CPU side optimization, there are works to reduce the memory footprint for CNN while running on a CPU. More precisely, Matveev et al. showed how to run connectomics <sup>1</sup> application on small multicore machines (with less than 100 cores) rather than a huge cluster of CPUs and GPUs.

### 3.2.2 Software Optimization for GPUs

As we mentioned, DL algorithms rely on linear algebra significantly. Due to their SIMD (Single Instruction stream Multiple Data stream) architectures, GPUs are excellent

<sup>&</sup>lt;sup>1</sup>Connectomics is a field of studying brain's connection by image processing of brain images.

fits for such applications. In SIMD architecture, one stream of control instructions instructs multiple functional units, which enable power-efficient massive parallel programming. In addition, GPUs allocate most of their real estate to ALUs rather than on-chip caches. In this section, we look into some of the GPU primitives used and customized for DNNs.

As we mentioned, DNNs rely on linear algebra functions. cuBLAS is the CUDA implementation of BLAS specification. ViennaCL is an openCL based library, which is able to run on CPUs, GPUs, and Xeon Phis. It can outperform cuBLAS in sparse matrix multiplications. MAGMA is a library for linear algebra with the goal of achieving fast implementation on hybrid/heterogeneous architectures.

There are also Python modules and wrappers for basic linear algebra primitives. Gnumpy [181] and CudaMat [131] are two examples. Gnumpy provides a GPU implementation for the popular Numpy Python library. Cudamat enables running CUDA kernels from a Python script. The combination and these two libraries can provide a simple environment for DNN development.

cuDNN is a library for DNNs built on Nvidias GPU [33]. It is also serves as a set of function specifications for DL basic functions. cuDNN provides an implementation of batched convolution optimized for specific GPU with respect to convolution layer parameters. cuDNN has been integrated into Caffe framework and leads to 36

Similar to cuDNN, AMD Radeon, another major GPU card vendor, has also provided a DNN framework. AMD takes advantage of Berkeley Caffe and replaced its CUDA code with its own HIP code [10].

In addition to running convolution in the time domain, one can perform it in the frequency domain [124], [187]. In the frequency domain, convolution is translated into element-wise multiplication. Lavin and Gray used the Winograd algorithm to reduce the number of multiplication in the FFT-base implementation of convolution layer [99]. In addition to CNN layers, there are works accelerating other layers on GPUs. For example, Ly et al. proposed a solution to run RBMs (Restricted Boltzmann Machines) on the GPUs [118]. There are also some projects targeting scalability by running DNNs over multiple GPUs. dMath provides a library to run linear algebra algorithm in multiple possibly heterogeneous GPUs [55]. Coates et al. used a cluster of GPUs to train a network with more than 11 billion parameters [37]. Hauswald et al. proposed DjiNN a WSC (Warehouse

Scale Computer) service for DL networks [71]. They have also shown that WSCs enabled by GPU can improve TCO (Total Cost of Ownership) by up to 40x compared to CPU-only WSCs.

vDNN addressed the memory limitation on GPUs for training mode [154]. GPUs rely on low-capacity but high bandwidth memory such as GDDRs and HBMs. However, training DNNs requires a huge amount of memory to store weights updates. vDNN virtualized CPU-side high capacity memory for the GPUs. vDNN achieves this by using a software prefetching scheme that delivers each layer's variables when they are needed. vDNN removes the memory capacity barrier with less than 18% performance loss compared to expensive high-capacity GPUs.

### 3.2.3 Deep Learning Frameworks

On top of the library for CPUs and GPUs, researchers developed a framework to simplify modeling and programming a new DL network. In this section, we review some of these frameworks.

Theano is a Python library for the multidimensional array which runs on both CPUs and GPUs and is particularly used for DNNs [12]. Developed at the University of Montreal, Pylearn2 is a DL library built on top of Theano [65]. Alex Krichevsky developed cuda-convnet, a fast c++/CUDA for DL networks and is scalable to multiple GPUs [96]. Zlateski et al. introduced ZNN, a large scale framework for shared memory system for CPU architectures. Caffe is another DL framework that targets speed and modularity [210]. Caffe supports both CPUs and GPUs and can run on top of cuDNN. Caffe supports varieties of layers, loss functions, weight update optimizations. Ristretto is built on top of Caffe to provide fixed point weights and to optimize the precision of these weights [68]. The industry has also contributed to the field by releasing their DL frameworks. Preferred Network America introduced Chainer that takes advantage of define-by-run paradigm. More specifically, Chainer memorizes the computational graph during the forward path and then uses this knowledge for the backward path of training [182]. Facebook also made its DL framework, Torch, available to the public. Torch provides an efficient implementation of neural network layers on both CPUs and GPUs. It also provides a high-level abstraction to these layers via C, Lua, and Python interfaces [39].

The other popular framework is Google's TensorFlow developed by Google Brain Team [4]. TensorFlow looks in the DNNs as graphs of computation. TensorFlow is able to run on a variety of platforms ranging from mobile devices to high-end GPUs. Intel also provides software for DL development. Intel Nervanas framework Neon is one example [136]. Neon outperforms most of the above frameworks for most of the layers used in DL algorithms [1]. Microsoft also introduced its CNTK (Cognitive ToolKit). Microsoft claims up to 10x speedup on recurrent neural networks compared with Google's TensorFlow [183]. Microsoft also embedded many innovative schemes for scalability of its framework, particularly in training mode.

Shi et al. compared some of these popular DL frameworks for different types of networks and on different hardware [167]. They have found that in many of these frameworks the benefits of scaling from 4 CPU cores to 16 cores is marginal. In addition, they found that Caffe, TensorFlow, and CNTK work the best for CNNs, fully connected Networks, and RNNs, respectively.

There are also some projects that specifically target scalability. BigDL is DL framework that distributes high-level model, written in Python and Scala, over Apache Spark cluster [20]. MXNet supports four front-end languages (i.e., Python, R, Julia, and Go) and runs on both GPUs and CPUs [135]. For GoogleNet network, it shows superlinear speedup. Before launching TensorFlow, Google deployed DistBelief for its large-scale projects. This framework supports an asynchronous stochastic gradient descent, named downpour SGC, for distributed training [45]. Microsoft also launched Project Adam, a distributed system for training very large DL networks. Adam balances the load over different components of the system to achieve an efficient implementation [35]. Twitter showed a machine learning software in their Hadoop-based platform [108]. SparkNet and DeepSpark are two frameworks for DL algorithms training over Spark, which is a MapReduce like distributed platform [87]. Cui et al. introduced GeePS that facilitates training on multiple GPUs that can accelerate single-GPU training by 9.5x with 16 GPU machines [43]. Neurosurgeon is a new tool that looks into the cloud-only processing of DL algorithms (e.g., Apple Siri and Google Now) from mobile applications [83]. It provides a computation partitioning over both cloud and mobile devices to optimize latency and energy consumption.

### 3.2.4 Approximation Approach

In the prior section, we reviewed prior works that try to manage the underlying hard-ware for running DNNs more efficiently. In this section, we look into a new category of works that approximate a network such that it requires less computation, demands lower memory bandwidth, or occupies smaller capacity. There are multiple approaches to reducing the computation of DL networks as described in the following subsection.

### 3.2.4.1 Compression

Memory capacity and bandwidth are the key performance and power bottlenecks of DNNs. Although hardware lossless compression mechanisms can seamlessly reduce this pressure, software solutions can outperform them [164]. To this end, software solutions might retrain the network to adjust for the loss due to compression. In addition, software solutions are superior as a DNN runtime is deterministic and does not need dynamic solutions based on predictions. Here we review some of these software approaches. Deep Compression showed that on top of its other techniques to reduce redundancy, Huffman coding can boost compressibility from 31x down to 49x [166]. Ko et al. proposed a JPEG encoding for the neural network weights. Their approach adjusts the level of quantization based on the error sensitivity of the weights [94]. Koutnik et al. reduce the number of parameters to learn in RL (reinforcement learning) algorithms by converting the weight matrix into the frequency domain and removing high-frequency values [95]. To improve their approach wavelet-based coding weights in the frequency domain have also been proposed [85].

#### **3.2.4.2** Pruning

Another approach to removing the DNN redundancy is to prune weights. Le Cun et al. proposed optimal brain damage (OBD) as an automatic network minimization technique for better generalization of a network with fewer training samples [104]. OBD tries to remove weights that would affect the error rate during training mode the least. Their approach reduces the number of weights by a factor of two. Collins and Kohli showed that using regularizer that promotes sparsity can reduce the number of weights by 4x with around 2% reduction in the accuracy [38]. Liu et al. demonstrate sparse decomposition to reduce unnecessary weights using their efficient implementation of sparse networks,

SCNN (Sparse CNN). They reported less than 1% reduction in the accuracy for removing 90% of the weight [110]. Han et al. proposed pruning followed by retraining to reduce the weights overhead by up to 13x without any loss in the network accuracy [70]. Guo et al. proposed an on-the-fly approach to prune connections that outperforms prior approaches both in compression rate and the number of pruning-training iterations [66]. Liu and Turakhia showed that by pruning of weights in the frequency domain, one can reduce the number of weights by up to 90% in LeNet [116]. Later, researchers proposed structured sparse networks to be more compatible with sparse matrix representation format. Lebedev and Lempitsky proposed a group-wise version of OBM that reduces the operation to smaller but dense matrices [102]. Wen et al. proposed SSL (Structured Sparsity Learning), an approach to make the sparse networks both compact and hardware-friendly [192]. With the same premise, Anwar et al. also showed that intrakernel sparsity with strides can reduce the redundancy dramatically [14]. Mao et al. observed that coarse-grain sparsity is both more hardware-friendly and compressible compared to fine-grain sparsity. In their work, they investigate the tradeoff between granularity and network accuracy [121]. Finally, Han et al. showed that sparsity can improve the accuracy of dense networks by up to 4.3%. To this end, they trained the network three times one as a dense network, then as a sparse one and again as a dense one. In the last dense training, they returned back the removed sparse weights and initialized them to zero [166].

### 3.2.5 Clustering

The other way to reduce the network redundancy is to cluster similar parameters together and replace all of them with one parameter. Nowlan and Hinton proposed a regularization to shape the networks such that the distribution of weight values fits into multiple Gaussians. Then they clustered similar weights. In their approach, clustering happens during training [139]. HashedNet implemented clustering by grouping the weights using hash functions. It then allocates one parameter to all the weights colliding to the same bucket [29]. BHNN structured the hashing mechanism to providing spatial locality for computation and hardware-friendliness while achieving 10x compressibility [208]. A similar idea to HashedNet has been proposed in FreshNets to cluster weights in the frequency domain representation [30]. Deep Compression applied weight sharing by categorizing

weights in multiple bins and allocating one value to all of them [166]. DivNet used determinantal point process (DPP) for each layer to model the diversity of neurons. The diversity is used then as a metrics to categorize similar neurons [123].

### 3.2.5.1 Matrix Reparametrization

Matrix reparametrization is a matrix approximation technique to reduce the capacity and computation requirements of matrix operations. In this approach, one large matrix is decomposed into the product of multiple smaller ones. Danil et al. discovered that deep learning networks are over-parameterized. They showed that with only 5% of the weight, one can predict the rest of them, accurately [46]. Inspired by this work, Gong et al. factorized weight matrix using singular-value decomposition [64]. They achieved up to  $24 \times$  compression with no more than 1% loss in accuracy. Zhang et al. proposed an optimization solution to minimize the reconstruction error for nonlinear layers subject to lower number ranks, which leads to  $4 \times$  speedup with only 0.9% loss in accuracy [204]. Jaderberg et al. reshape the CNN layers by decomposing its 2D filters into 1D filters and achieved  $2.5 \times$  and  $4 \times$  speedup with no loss and 1% loss in accuracy, respectively [78]. Similarly, Denton et al. proposed a low-rank solution with 2x speedup and 1% accuracy loss [47]. They used a low-rank approximation that minimizes the distance between the original and constructed matrices. To this end, they introduced a new metric that magnifies error-sensitive weights more than others. Similarly, a CP-decomposition ( Canonical Polyadic decomposition) has been proposed with the same speedup-accuracy loss tradeoff [101]. Deep Fried Convnets targeted the huge fully-connected layers and uses adaptive Fastfood transform to reduce the number of parameters from O(nd) to O(n) where d and n are the numbers of input and output neurons in a fully-connected layer. In the Fastfood transform, the Matrix W representing FC-layer will be approximated with SHGPHP where S, G, and B are diagonal matrices, P is a random permutation matrix, and H is the Walsh-Hadamard matrix, respectively. Novikov et al. show a matrix tensorization approach that reduces the FC-layer capacity by five orders of magnitudes at the cost of 2% loss in accuracy. In this approach, the original matrix is reshaped into a multidimensional tensor. Each element of the tensor is a product of multiple small matrices [138]. Using the same concept, Garipov et al. extended ternsorizing for the entire network and achieved  $80 \times$  compression. The similar concept used in [18] to provide a lookup-based CNN. Besides decomposition to smaller matrices/vectors, Sindhwani et al. proposed using structured matrices. In these matrices, a few values repeat in multiple entries. Using displacement operators, it is possible to transform such matrices to low-rank ones [169].

#### 3.2.5.2 Quantization

The quantization of DNN weights has been considered to simplify hardware acceleration. Feisler et al. used quantization for optical neural networks since the number of intensity level in optics were limited to a few levels [59]. At the cost of the loss in accuracy, they considered a set of integer values for the weights in each layer. Xie and Jabri took advantage of a statistical quantization model (i.e., quantization as an error to the real value) to investigate the effect of the number of bits, the number of layers on the error due to quantization [195]. Based on their findings, they later proposed a combined search algorithm which has two parts: Modified Weight Perturbation (MWP) and Partial Random Search (PRS). MWP uses gradient check to find the direction of updating while PSR adds randomness by randomly changing a weight value if it leads to a smaller error. With these techniques, they achieved the same accuracy as the unlimited precision with only 8-bit to 10-bit fixed point number representations [196]. Tand and Kwan quantized in three phases: training, quantizing, and adjusting. In the quantizing phase, they just limited the weight to be zero or a powers-of-two. Later in the adjusting phase, they minimized the error by tuning the slope of the activation functions. In their evaluations, they could reduce the number of values per weight to six numbers with no more than 3% accuracy loss [180]. Dundar et al. improved prior statistical models used by considering nonlinearity in their model [52]. Draghici and Sethi theoretically showed the capability of integer weights for classification [50] [49]. Alippi and Briozzo extended prior works on the accuracy loss analysis due to quantization to cover cases with low fan-in neurons such as sparse NNs [8]. Based on the interval arithmetic, Anguita et al. proposed a method to derive the worst-case error due to quantization [13]. In their analysis, they considered a quantized number as an interval around the real value and the size of the interval is assumed to be the quantization error. This consideration made their approach independent of the input data distribution.

All the abovementioed works investigated quantization for MLP. Since DNNs demand high computations, quantization has also reapplied in the recent years. Hwang and Sung used a backpropagation-based training to compress the weights to three cases (-1,0,+1). For MNIST and TIMIT dataset, they observed a negligible loss in the accuracy [77]. To reduce the overhead of multiplications in DNNs, Courbariaux et al. proposed a low-precision training solution for fixed point, floating point and dynamic fixed point operations [41]. In their approach, they used low-precision operations during the forward and backward propagations while using high-precision operations for updating the weights. For the maxout network, they found that 10 bits per weights are enough. Gupta et al. observed the critical role of rounding in low-precision fixed-point DNNs [67]. In their work, they replaced the round-to-nearest approach with the stochastic rounding. In the stochastic rounding, the distance between a floating point number and its fixed point neighbors are used as a probability to round the floating point number to one of two neighbors. For floating point numbers outside the boundary of the fixed point range, they assigned the corresponding fixed point bound [90]. They proposed BNN (Bitwise Neural Networks) with binary and ternary weights [109]. In their approach, based on the observation that activation values are less sensitive to the error than the gradients, they considered floating point gradient and power-of-two activation values for backpropagation. Lin et al. have proposed a binary neural network derived from a real-valued one. The real-valued NN's weights are restricted to [-1,+1] using tanh function. In their approach, they zeroed some connections and the number of zeroed connections is a hyper parameters. XNOR-net approximated a weight matrix as a product of some trainable floating point quotient and a bipolar matrix. They minimized the error between the original matrix and the approximated one by assigning the sign value of the original weights to the binary matrix's entities and the average of the weights value to the matrix quotient. BNN or (Binarized Neural Networks) has been proposed to take advantage of hard sigmoid function, which is a stochastic sign function for stochastic binarization of the weights. To avoid gradients vanishing, they used straight-through estimator [42]. Miyashita et al. logarithmic representation of weights and activation function outputs. The logarithmic representation can reduce the multiplication operations to shifts and adds. They also

showed a simple approximation for adding logarithmic values. TWN (Ternary Weight Networks) approximated the original weight matrix with the product of a ternary matrix and a floating point quotient. They proposed to find ternary weights by optimizing the Euclidian distance of the original and the approximated matrices [106]. TTQ (Trained Ternary Quantization) used ternary weights and two floating point quotients ( $W_n$  and  $W_p$ ) [206]. the entities with the value -1(+1) are multiplied by  $W_n(W_p)$ . They also considered a trainable threshold  $W_t$  for quantizing weights to -1, 0, and +1. DoReFa-Net proposed a general framework with different precisions for the weights, activation values, and gradients [205]. With a negligible additional error, they trained AlexNet with 6-bit gradients.

#### **3.2.6 Summary**

We review many software approaches for the efficient implementation of DNNs. We believe that the approximation techniques presented so far can also be applied to our in-situ computing accelerators (discussed in Chapter 4 and 5). Furthermore, we think that, with the emergence of hardware accelerators in the future, the software frameworks reviewed here will be very helpful to program and manipulate these hardware units.

# 3.3 Hardware Approach

The neural networks, compared to many other machine learning solutions such as SVM (support vector machine), are computation intensive. As a result, there have been many hardware acceleration proposals for neural networks. In this section, we review some of these implementations for Digital ASICs, FPGA, and Analog ASICs.

#### 3.3.1 Digital ASICs

Treleaven et al. [184] covered some of the earlier work on the hardware implementation of neural networks such as Netsim [176] and WISARD for image recognition. Nordstrom and Svensson looked into a different way to parallelize large neural networks and concluded that a ring-based network of SIMD architectures can achieve high utilization [137]. Holi and Hwang offered a theoretical analysis to find the best precision for fixed-point neural network implementations [75].

In the last few years, DNNs have shown dramatic accuracy improvement in many applications. This motivated many new implementations for neural networks. Chakradhar