# HARNESSING GPU COMPUTING IN SYSTEM-LEVEL SOFTWARE

by

Weibin Sun

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

${\rm in}$

Computer Science

School of Computing

The University of Utah

August 2014

Copyright © Weibin Sun 2014

All Rights Reserved

# THE UNIVERSITY OF UTAH GRADUATE SCHOOL

# STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                |                                   |                |

|------------------------------------|-----------------------------------|----------------|

| has been approved by the following | ng supervisory committee members: |                |

|                                    |                                   |                |

| Robert Ricci                       | , Chair                           | May 1, 2014    |

|                                    |                                   | Date Approved  |

| Jacobus van der M                  | Ierwe , Member                    | May 1, 2014    |

|                                    |                                   | Date Approved  |

| John Regehr                        | , Member                          | May 1, 2014    |

|                                    |                                   | Date Approved  |

| Mary Hall                          | , Member                          | May 1, 2014    |

|                                    |                                   | Date Approved  |

| Eddie Kohler                       | , Member                          | May 1, 2014    |

|                                    | ·                                 | Date Approved  |

| and bu                             | Dogg Whiteless                    | Chair of the   |

| and by                             | Ross Whitaker                     | , Chair of the |

| School of                          | Computing                         |                |

|                                    |                                   |                |

and by David B. Kieda, Dean of The Graduate School.

#### ABSTRACT

As the base of the software stack, system-level software is expected to provide efficient and scalable storage, communication, security and resource management functionalities. However, there are many computationally expensive functionalities at the system level, such as encryption, packet inspection, and error correction. All of these require substantial computing power.

What's more, today's application workloads have entered gigabyte and terabyte scales, which demand even more computing power. To solve the rapidly increased computing power demand at the system level, this dissertation proposes using parallel graphics processing units (GPUs) in system software. GPUs excel at parallel computing, and also have a much faster development trend in parallel performance than central processing units (CPUs). However, system-level software has been originally designed to be latency-oriented. GPUs are designed for long-running computation and large-scale data processing, which are throughput-oriented. Such mismatch makes it difficult to fit the system-level software with the GPUs.

This dissertation presents generic principles of system-level GPU computing developed during the process of creating our two general frameworks for integrating GPU computing in storage and network packet processing. The principles are generic design techniques and abstractions to deal with common system-level GPU computing challenges. Those principles have been evaluated in concrete cases including storage and network packet processing applications that have been augmented with GPU computing. The significant performance improvement found in the evaluation shows the effectiveness and efficiency of the proposed techniques and abstractions. This dissertation also presents a literature survey of the relatively young system-level GPU computing area, to introduce the state of the art in both applications and techniques, and also their future potentials.

# CONTENTS

| $\mathbf{A}\mathbf{B}$ | BSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                        | iii                                                                        |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| LIS                    | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                  | vii                                                                        |

| LIS                    | ST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                   | viii                                                                       |

| AC                     | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                                                         |

| СН                     | IAPTERS                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 1.                     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                          |

|                        | 1.1 Dissertation Statement1.2 Contributions1.3 Findings1.4 Dissertation Outline                                                                                                                                                                                                                                                                                                                                                                | 3<br>3<br>5                                                                |

| 2.                     | GENERAL PURPOSE GPU COMPUTING                                                                                                                                                                                                                                                                                                                                                                                                                  | 6                                                                          |

|                        | 2.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6<br>7<br>8<br>9<br>10                                                     |

| 3.                     | SYSTEM-LEVEL GPU COMPUTING PRINCIPLES                                                                                                                                                                                                                                                                                                                                                                                                          | <b>12</b>                                                                  |

|                        | 3.1 Throughput-oriented Architecture 3.1.1 Parallel Workload Abstraction 3.1.2 Avoid Control Flow Divergence 3.2 Coalesce Global Memory Accesses 3.3 Overlapped GPU Operations 3.4 Asynchronous GPU Programming 3.5 Reduce Memory Copy Overhead 3.5.1 DMA Overhead 3.5.2 Avoid Double-buffering 3.5.3 Trade Off Memory Copy Costs 3.5.4 Discussion 3.6 Miscellaneous Challenges 3.6.1 Kernel-User Communication 3.6.2 Implicit Synchronization | 13<br>13<br>14<br>16<br>16<br>17<br>18<br>19<br>20<br>20<br>21<br>21<br>21 |

|                        | 3.7 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22                                                                         |

| <b>4.</b>  | GPUSTORE: GPU COMPUTING FOR STORAGE         | <b>23</b> |

|------------|---------------------------------------------|-----------|

|            | 4.1 Design                                  | 23        |

|            | 4.1.1 Overview                              | 23        |

|            | 4.1.2 Memory Management                     | 25        |

|            | 4.1.3 Request Management                    | 26        |

|            | 4.1.4 Streams Management                    | 28        |

|            | 4.2 Implementation                          | 28        |

|            | 4.3 Evaluation                              | 29        |

|            | 4.3.1 Framework Performance                 | 29        |

|            | 4.3.2 Encrypted Device Mapper               | 30        |

|            | 4.3.3 Encrypted File System                 | 31        |

|            | 4.3.4 Data Recovery                         | 34        |

|            | 4.4 Summary and Future Work                 | 36        |

| <b>5</b> . | SNAP: PACKET PROCESSING WITH CLICK AND GPUS | 37        |

|            | 5.1 Click Background                        | 38        |

|            | 5.2 Motivating Experiments                  | 38        |

|            | 5.3 Design                                  | 41        |

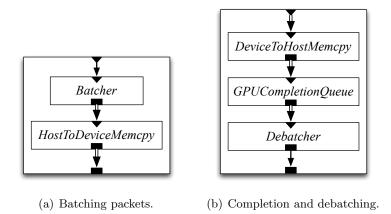

|            | 5.3.1 Batched Packet Processing             | 41        |

|            | 5.3.2 Packet Processing Divergence          | 46        |

|            | 5.3.3 Asynchronous Processing               | 48        |

|            | 5.3.4 Packet I/O                            | 49        |

|            | 5.4 Implementation                          | 50        |

|            | 5.5 Evaluation                              | 51        |

|            | 5.5.1 Packet I/O                            | 52        |

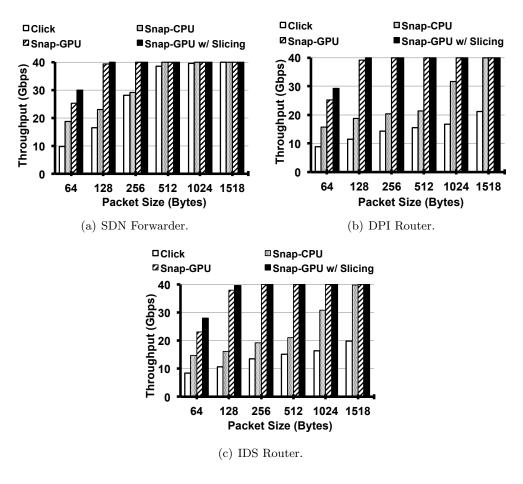

|            | 5.5.2 Applications                          | 52        |

|            | 5.5.3 Latency and Reordering                | 54        |

|            | 5.5.4 Packet Processing Divergence          | 55        |

|            | 5.5.5 Flexibility and Modularity            | 55        |

|            | 5.6 Summary and Future Work                 | 58        |

| 6.         | A SURVEY OF SYSTEM-LEVEL GPU COMPUTING      | 60        |

|            | 6.1 Applications                            | 61        |

|            | 6.1.1 Networking                            | 61        |

|            | 6.1.2 Storage                               | 63        |

|            | 6.1.3 Database Processing                   | 64        |

|            | 6.1.4 Security                              | 65        |

|            | 6.1.5 Program Analysis                      | 65        |

|            | 6.1.6 Data Compression                      | 66        |

|            | 6.2 Techniques                              | 66        |

|            | 6.2.1 Batched Processing                    | 67        |

|            | 6.2.2 Memory Copy Overhead                  | 67        |

|            | 6.2.3 Warp Divergence                       | 70        |

|            | 6.2.4 Improve GPU Utilization               | 70        |

|            | 6.2.5 Virtualization and Migration          | 71        |

|            | 6.2.6 Resource Management and Scheduling    | 71        |

|            | 6.3 Future                                  | 72        |

|            | 6.4 Summary                                 | 73        |

| 7.            | CONCLUSIO | ON . | <br> | <br> | <br> | <br> |  | <br> | <br> |  | <br> | <br> | <br> |  | 75 |

|---------------|-----------|------|------|------|------|------|--|------|------|--|------|------|------|--|----|

| $\mathbf{RE}$ | FERENCES  |      | <br> | <br> | <br> | <br> |  | <br> | <br> |  | <br> | <br> | <br> |  | 77 |

# LIST OF FIGURES

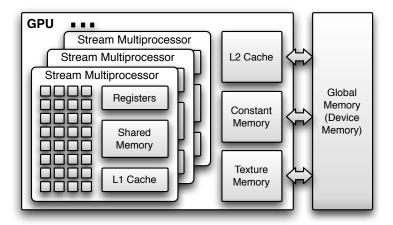

| 2.1  | Architecture of a CUDA GPU                                                                                                                                                                                        | 7  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

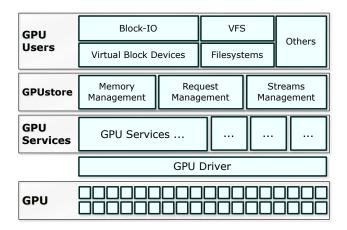

| 4.1  | The architecture of GPUstore                                                                                                                                                                                      | 24 |

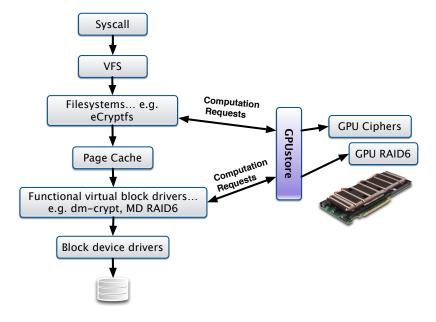

| 4.2  | The workflow of a GPUstore-based storage stack                                                                                                                                                                    | 24 |

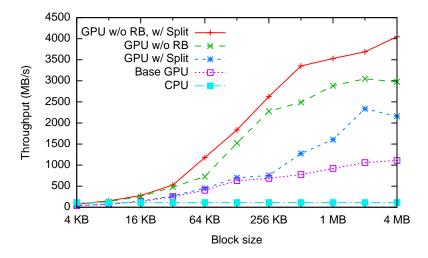

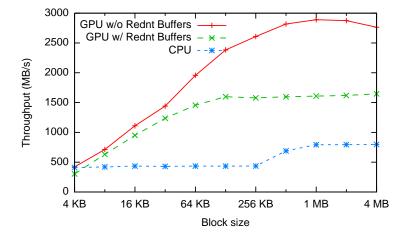

| 4.3  | GPU AES cipher throughput with different optimizations compared with Linux kernel's CPU implementation. The experiments marked "w/o RB" use the techniques described in Section $4.1.2$ to avoid double-buffering | 25 |

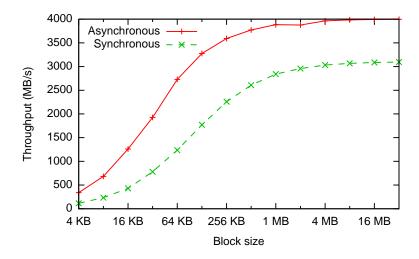

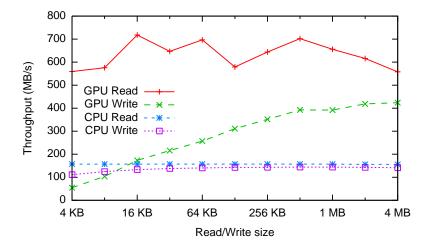

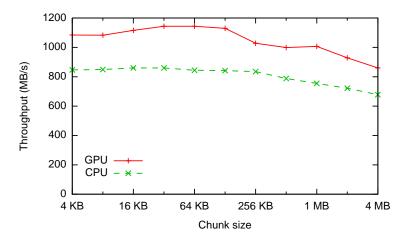

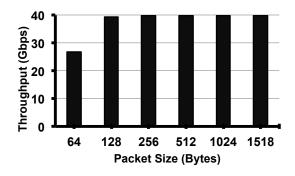

| 4.4  | Throughput of a GPU kernel that copies data but performs no computation                                                                                                                                           | 30 |

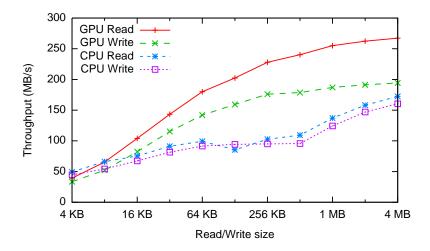

| 4.5  | dm-crypt throughput on an SSD-backed device                                                                                                                                                                       | 31 |

| 4.6  | dm-crypt throughput on a DRAM-backed device                                                                                                                                                                       | 31 |

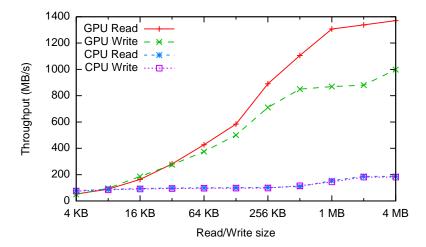

| 4.7  | eCryptfs throughput on an SSD-backed file system                                                                                                                                                                  | 32 |

| 4.8  | eCryptfs throughput on a DRAM-backed file system                                                                                                                                                                  | 32 |

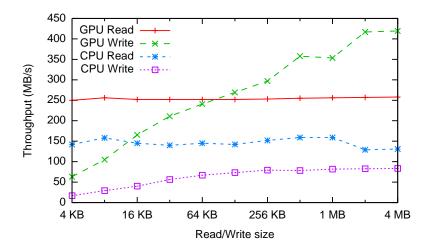

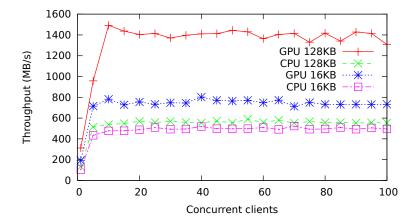

| 4.9  | ${\tt eCryptfs}$ concurrent write throughput on a DRAM disk for two block sizes                                                                                                                                   | 34 |

| 4.10 | Throughput for the RAID recovery algorithm with and without optimizations to avoid redundant buffers                                                                                                              | 34 |

| 4.11 | RAID read bandwidth in degraded mode                                                                                                                                                                              | 35 |

| 4.12 | RAID read bandwidth in degraded mode on DRAM-backed devices                                                                                                                                                       | 35 |

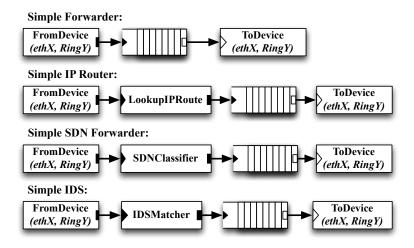

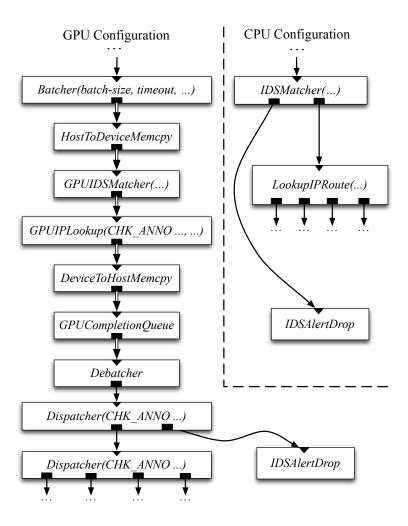

| 5.1  | Simplified Click configurations for motivating experiments                                                                                                                                                        | 39 |

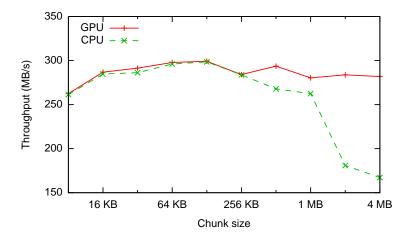

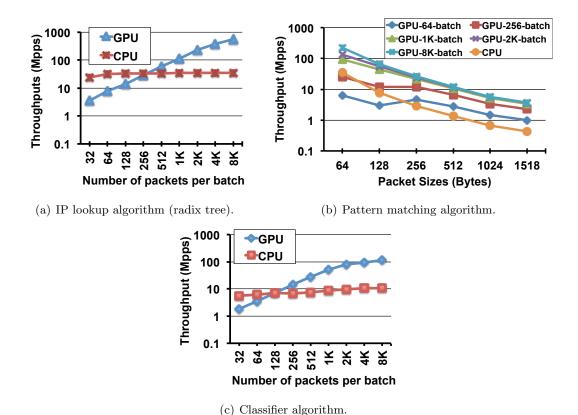

| 5.2  | GPU versus CPU performance on packet processing algorithms. Note that the axes are nonlinear                                                                                                                      | 40 |

| 5.3  | The PacketBatch structure                                                                                                                                                                                         | 43 |

| 5.4  | A slicing example                                                                                                                                                                                                 | 44 |

| 5.5  | Batching and debatching elements. Serial interfaces are shown as simple arrows, wide interfaces as double arrows                                                                                                  | 45 |

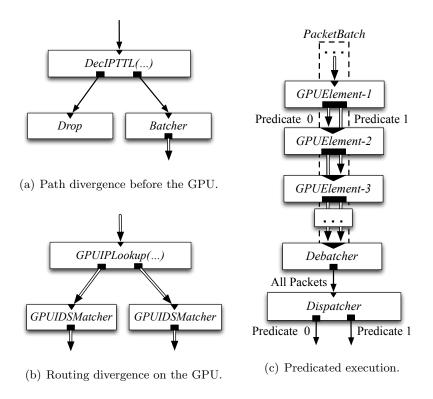

| 5.6  | Handling divergent packet paths                                                                                                                                                                                   | 47 |

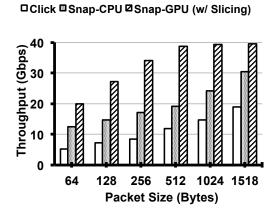

| 5.7  | Application performance                                                                                                                                                                                           | 53 |

| 5.8  | Forwarding performance when using a GPUSDNClassifier that diverges to two GPUIDSMatcher elements.                                                                                                                 | 56 |

| 5.9  | Major changes of the standard Click router to build a GPU-based IDS router.                                                                                                                                       | 57 |

| 5.10 | Fully functional IP router + IDS performance                                                                                                                                                                      | 57 |

# LIST OF TABLES

| 4.1 | Modified lines of code (LOC) to use GPUstore        | 29 |

|-----|-----------------------------------------------------|----|

| 5.1 | Relative throughputs of simple processing pipelines | 40 |

| 5.2 | Base forwarding performance of Snap and Click       | 53 |

#### ACKNOWLEDGMENTS

I want to thank my parents and my grandparents, who always give me the freedom to choose my life and always encourage me to pursue my dream.

Endless thanks to my wife Shuying, who always gives me a backup and cheers me up in any circumstances. She also listened to my practice talks every day during the week before the defense and gave me valuable comments and suggestions to improve my slides and presentation style. Thank you, for loving me!

I want to thank my daughter, Maggie. She is the main reason that drives me to graduate! She gives us endless laughter and tears.

Many thanks to my advisor, Robert Ricci. I cannot use a finite number of words to express my thanks to him. He is the best advisor and friend you can imagine! He listens to my strange ideas, supports me to study and do research on them, writes funding proposals for my project, modifies and refines every word of my awkward English paper drafts, gives me comments and suggestions on each single slide of my presentations... Thank you, for guiding me!

I also want to thank my friend and office-mate Xing. We discussed a lot on my research project, papers, dissertation and presentations, which helps me make this work. Thank you for your help in both study and life as my neighbor!

Special thanks to Mary Hall, who is also in my committee. I learned GPU programming and various techniques from Mary's class. Without her class, I would not be able to do this work at all. Mary also wrote a recommendation letter for me to help me get the NVIDIA fellowship, which funded part of my research. So, also thank NVIDIA!

I also want to thank my other committee members: John, Kobus and Eddie. John may be not aware of the fact that I started learning the low-level bus details because of his embedded class, where he showed us how easy the low-level hardware and principle is. Kobus gave me useful suggestions on how to improve my dissertation. He also helped me with my Snap paper's publication, which makes me qualified for graduation. Eddie developed the Click modular router, without which Snap cannot exist at all!

There are more people that I should thank. Mike, who was always helpful when I did experiments; Gary, who helped editing my papers; Eric, the LaTeX guru that helped my papers, and also my presentations; Ren, who helped me with English grammars and words, and many other people who helped me in Flux or in school of computing.

## CHAPTER 1

## INTRODUCTION

System-level software sits at the bottom of the software stack, including file systems, device drivers, network stacks, and many other operating system (OS) components. They provide basic but essential storage, communication and security functionalities for upper-level applications. It is vital for system software to make those functionalities efficient and scalable, otherwise the entire software stack will be slowed down. Yet, many system-level functionalities require substantial computing power. Examples include encryption for privacy, deep packet inspection for network protection, error correction code or erasure code for fault tolerance, and lookups in complex data structures (file systems, routing tables, or memory mapping structures). All of these may consume excessive processing power. What's more, today's application workloads are dramatically increasing: gigabytes or even terabytes of multimedia contents, high definition photos and videos, tens or even hundreds of gigabits per second network traffic and so on. Thus more and more computing power is needed to process those bulk-data workloads on modern rich functional software stacks.

A very common and important feature of many system-level computational functionalities is that they are inherently parallelizable. Independent processing can be done in parallel at different granularities: data blocks, memory pages, network packets, disk blocks, etc. Highly parallel processors, in the form of graphics processing units (GPUs), are now common in a wide range of systems: from tiny mobile devices up to large scale cloud server clusters [1] and super computers [2]. Modern GPUs provide far more parallel computing power than multicore or many-core central processing units (CPUs): while a CPU may have two to eight cores, a number that is creeping upwards, a modern GPU may have over two thousands [3], and the number of cores is roughly doubling each year [4]. As a result, exploiting parallelism in system-level functionalities to take advantage of today's parallel processor advancement is valuable to satisfy the excessive demand of computing power by modern bulk-data workloads.

GPUs are designed as a throughput-oriented architecture [5]: thousands of cores work

together to execute very large parallel workloads, attempting to maximize the total throughput, by sacrificing serial performance. Though each single GPU core is slower than a CPU core, when the computing task at hand is highly parallel, GPUs can provide dramatic improvements in throughput. This is especially efficient to process bulk-data workloads, which often bring more parallelism to fully utilize the thousands of GPU cores.

GPUs are leading the way in parallelism: compilers [6, 7, 8], algorithms [9, 10, 11], and computational models [12, 13, 14] for parallel code have made significant advances in recent years. High-level applications such as video processing, computer graphics, artificial intelligence, scientific computing and many other computationally expensive and large scale data processing tasks have benefited with significant performance speedups [15, 16] from the advancement of parallel GPUs. System-level software, however, have been largely left out of this revolution in parallel computing. The major factor in this absence is the lack of techniques for how system-level software should be mapped to and executed on GPUs.

For high-level software, GPU computing is fundamentally based on a computing model derived from the data parallel computation such as graphics processing and high performance computing (HPC). It is designed for long-running computation on large datasets, as seen in graphics and HPC. In contrast, system-level software is built, at the lowest level of the software stack, on sectors, pages, packets, blocks, and other relatively small structures despite modern bulk-data workloads. The scale of the computation required on each small structure is relatively modest. Apart from that, system-level software also has to deal with very low-level computing elements, such as memory management involving pages, caches, and page mappings, block input/output (I/O) scheduling, complex hardwares, device drivers, fine-grained performance tuning, memory optimizations and so on, which are often hidden from the high-level software. As a result, system-level software requires technologies to bridge the gap between the small building structures and the large datasets oriented GPU computing model; also to properly handle those low-level computing elements with careful design trade-offs and optimizations, to take advantage of the parallel throughput-oriented GPU architecture.

This dissertation describes the generic principles of system-level GPU computing, which are abstracted and learned from designing, implementing and evaluating general throughput-oriented GPU computing models for two representative categories of system-level software: storage applications and network packet processing applications. Both models are in the form of general frameworks that are designed for seamlessly and efficiently integrating parallel GPU computing into a large category of system-level software. The principles

include unique findings of system-level GPU computing features, and generic design techniques and abstractions to deal with common system-level GPU computing challenges we have identified. The significant performance improvements in storage and network packet processing applications brought by integrating GPU computing with our frameworks shows the effectiveness and efficiency of the proposed techniques and abstractions, and hence supporting the following statement:

## 1.1 Dissertation Statement

The throughput of system software with parallelizable, computationally expensive tasks can be improved by using GPUs and frameworks with memory-efficient and throughput-oriented designs.

#### 1.2 Contributions

The contributions of this dissertation work include the following.

- Two general frameworks, GPUstore [17] and Snap [18], for integrating parallel GPU computing into storage and network packet processing software, as described in Chapter 4 and Chapter 5.

- Three high throughput GPU-accelerated Linux kernel storage components, including a filesystem and two storage device mappers, which are discussed in Chapter 4.

- A set of Click [19] elements for Snap to help build parallel packet processing pipelines with GPUs, which are described in Chapter 5.

- A modified fully functional Click Internet protocol (IP) router with fast parallel GPU acceleration built on top of Snap as described in Chapter 5.

- A literature survey of system-level GPU computing that covers existing work, potential applications, comparison of the useful techniques applied in surveyed work and the ones proposed in our work as presented in Chapter 6.

# 1.3 Findings

Besides the above contributions, we also have found and learned valuable facts and lessons from designing and implementing GPUstore and Snap. We believe they are common and applicable to other system-level GPU computing software, too. We will thoroughly discuss them in the later chapters. For now, they are listed below as an overview.

• Batching improves GPU utilization. System code is often latency-oriented. As a result, system software often works with small building blocks. However, GPUs' architecture is throughput-oriented. Small building blocks lead to constant overhead

and low GPU utilization. To bridge the gap between the latency-oriented system code and throughput-oriented GPUs, batching small blocks to process many at once amortizes the overhead and improves GPU utilization. Batching may increase the processing latency of a single block, but for systems dealing with I/O, adding relatively small latency is tolerable.

- High throughput computing needs truly asynchronous GPU programming. With the required synchronization, current GPU programming models are mismatched to asynchronous system components, which widely exist in file systems, block I/O, device drivers, and network stacks at system level. Synchronization stalls the typical GPU computing pipeline which consists of three common stages: (1) host-to-device direct memory access (DMA) copy; (2) GPU kernel execution; (3) device-to-host DMA copy. Event-based or callback-based asynchronous GPU programming is necessary for asynchronous systems code, allowing it to fully utilize the GPU pipeline and achieve high throughput.

- System code has data usage patterns that are different from traditional GPU code. Traditional GPU computing usually reads the data from a file or the network into host memory, copies the entire data buffer into GPU device memory, and does the computation based on all the data. However, the code in a system component often works as a stage of a long data processing pipeline, and may use either the entire dataset passed through the pipeline, or just a few small pieces. In order to improve the system performance, special care must be taken to provide different memory models to system code (both the CPU side code and the GPU side code) according to the code's data usage pattern.

- The computation needs all the data. This data usage pattern is similar to traditional GPU computing. In this case, the GPU needs the entire dataset to be copied into GPU memory. To reduce the memory copy overhead, we should focus on reducing the copy within host memory. Different from traditional GPU computing, in the system-level context, processing stages often pass data buffers owned by a third party, such as the page-cache managed memory in the storage stack and network packet buffers in the network stack, through a long pipeline. Remapping the memory to make it GPU DMA-capable avoids redundant memory copy in host memory.

- The computation uses just a few small pieces of the large trunk of data. In contrast to most GPU computing, some system-level computing tasks

such as packet processing use only a few small pieces of the entire dataset. In this case, copying the entire dataset into GPU memory wastes a large portion of the bus bandwidth. Considering the much higher host memory bandwidth than the bus bandwidth, it is worth copying the scattered small pieces into a consecutive host memory buffer, allowing one smaller DMA copy to GPU. Such trade-off takes advantage of the faster host memory to reduce the overall memory copy time. Gathering the scattered pieces together also benefits memory access coalescing on the GPU, taking advantage of the wide GPU memory interface.

## 1.4 Dissertation Outline

Chapter 2 gives a simple background introduction of concepts, techniques and features of general purpose GPU computing. This chapter tries to get readers without GPU computing background familiar with it, and also defines the terminology used in later chapters. Readers familiar with traditional GPU computing can skip this.

Chapter 3 describes the system-level GPU computing principles at the high level. It discusses the challenges and special requirements in system-level GPU computing and the proposed techniques and abstractions to deal with them.

Chapter 4 describes the storage framework GPUstore, including the design, implementation and the experimental evaluation. The GPU-accelerated file system and block device drivers built on top of GPUstore have achieved up to an order of magnitude performance improvements compared with the mature CPU-based implementations.

Chapter 5 describes the network packet processing framework Snap, similar to the previous GPUstore, including the design, implementation and the experiments. The demonstrated deep packet inspection router built with Snap has shown 40 Gbps (gigabits per second) line rate packet processing throughput at very small packet size.

Chapter 6 is the survey of system-level GPU computing, which includes both existing work and the identified possible application areas. The survey discusses techniques used by other system-level GPU systems to compare with what this dissertation has proposed and applied.

Chapter 7 reviews the dissertation and concludes.

## CHAPTER 2

#### GENERAL PURPOSE GPU COMPUTING

This chapter describes essential general purpose GPU (GPGPU) computing background that is needed to help understand the rest of the dissertation. Currently, there are two most widely used GPGPU frameworks: compute unified device architecture (CUDA) [4] and open computing language (OpenCL) [20]. CUDA is a proprietary framework developed by NVIDIA corporation; OpenCL is a public framework designed by Khronos Group. Despite its proprietary feature, CUDA has several advanced features, such as concurrent streaming and flexible memory management which are helpful to system-level computing and OpenCL missed at the time of my dissertation work. As a result, CUDA is used in this dissertation to represent the lowest level GPGPU computing framework. And its terminology and concepts are used in this chapter to explain GPGPU computing. For a comprehensive description of CUDA-based modern GPGPU computing, readers may refer to NVIDIA's CUDA programming guide [4].

#### 2.1 Overview

A GPU works as a coprocessor of the CPU. It has dedicated video memory on the card to save the computing data. The processor cores on GPU can only access the video memory, so any data to be processed by the GPU must be copied into the video memory. To utilize the GPU, a typical workflow includes three steps:

- 1. CPU code copies the data to be processed from main memory (also called "host memory" in CUDA) to the video memory (also called "device memory");

- 2. CPU code starts the GPU kernel, which is the program to be executed on the GPU, to process the copied data and produce the result in the device memory;

- 3. After the GPU kernel execution, the CPU code copies the result from device memory back to host memory.

Most GPUs sit in the peripheral component interconnect express (PCIe) slots, needing DMA over PCIe for the aforementioned memory copy. The GPU kernel is a program consisting

of GPU binary instructions. Using CUDA, programmers can write C/C++ code, then use **nvcc** to compile them into GPU instructions. CUDA also provides runtime libraries to allow CPU code to use special host memory, device memory, make DMA copy and manage GPU execution.

## 2.2 Parallel GPGPU

A GPGPU is a special single instruction multiple data (SIMD) processor with hundreds or thousands of cores and a variety of memory types (as shown in Figure 2.1). On recent CUDA GPUs, each 32 cores are grouped into a "warp." All 32 cores within a warp share the same program counter. A GPU is divided into several "stream multiprocessors," each of which contains several warps of cores and fast on-chip memory shared by all cores. A GPU kernel is executed by all the physical cores in terms of threads. So for a given GPU kernel, it becomes one thread on each GPU core when executing. High-end GPU models, such as GTX Titan Black [3], can have as many as 2880 cores. In that sense, up to 2880 threads can concurrently run on a GPU to execute a single GPU kernel. Threads on GPU cores may do hardware-assisted context switching, in case of memory operations or synchronization, which is determined and scheduled by the GPU hardware. Such zero-cost hardware context switching makes it possible to run millions of threads on a single GPU without any context switching overhead. Such a "single kernel executed by multiple threads" computing model is called single instruction multiple threads, or SIMT.

SIMT is a simple and efficient parallel processor design. But similar to other SIMD processors, the performance of SIMT may suffer from any control flow divergence because of the shared program counter within a warp. On CUDA GPUs, any control flow divergence

Figure 2.1. Architecture of a CUDA GPU.

within a warp may cause serialized control flow. When a core executes the control flow branch that its current thread should not jump into, it simply disables memory or register access to disable the execute effects. Different from the powerful sequential cores on CPUs that are armed with large cache, out-of-order execution and accurate branching prediction, a single GPU core is very weak. The performance speedup of many GPGPU programs comes from partitioning the workload into millions of small pieces processed by thousands of lame cores in parallel. As a result, a GPU kernel full of such control flow structures may severely slow down the GPU performance due to the control flow divergence.

SIMT architecture requires programmers to carefully tune their GPU kernels to avoid conditional structures and to reduce as many loops as possible. This can affect the data processing design in system software. For example, when using GPUs to process a batch of network packets through the network stack, packets in the batch may diverge to different paths because of their different protocols. Such path divergence will lead to warp divergence on GPUs because GPU kernel threads must execute different code for packets going to different paths. As we will see in Snap, we have proposed techniques and design principles to reduce the overhead caused by this problem.

# 2.3 GPU Memory Architecture

The original video memory on GPU board has been largely increased to up to 6GB (gigabyte) for a single GPU. Compared with the instruction execution on GPU cores, accessing GPU video memory, which is also called global memory, is much slower and may cost hundreds of cycles. So global memory access is a time consuming operation that should be minimized. Fortunately, the GPU memory bus width is much wider than normal CPUs, e.g., some model [3] has a 384 bits memory bus width which leads to 336 GB/s bandwidth. Though a single thread may not be able to fully utilize the 384 bits bus, a SIMT-oriented GPU kernel may take advantage of the wide bus by issuing memory access operations to consecutive locations from the same warp, which is called "memory access coalescing."

Besides the global memory, there are some special memory types on GPUs for fast memory access in certain applications (as shown in Figure 2.1). Constant memory is a small region of memory that supports fast read-only operations. Texture memory is similar to constant memory but has very fast special access patterns. For example, according to the Kargus [21] network intrusion detection system (NIDS), using texture memory for deterministic finite atomata (DFA) transition table improves the pattern matching

performance by 20%. Shared memory can be viewed as a program-controlled cache for a block of threads. Its access latency can be 100x lower than the uncached global memory. In fact, current CUDA GPUs use a single region of 64KB (kilobyte) on-chip memory per stream multiprocessor to implement both layer one (L1) cache and shared memory, allowing either 48 KB cache and 16 KB shared memory or 16 KB cache and 48 KB shared memory split that is configurable by programmers. Besides program-controlled cache for fast frequent data access, shared memory can also be used to achieve global memory access coalescing, e.g., when using four threads to encrypt a single 16-byte advanced encryption standard (AES) data block, each thread can issue a four-byte read operation to be coalesced into a single sixteen-byte transaction.

As a result, to achieve high performance GPU computing, a GPU program should be designed and executed with the following memory related considerations: consecutive threads should issue coalescable memory accesses; memory access latency can be hidden by launching more threads than cores in order to switch out the threads that wait for memory transaction; read-only data should go into constant or texture memory; frequently accessed data should go into shared memory.

# 2.4 Advanced GPGPU Computing

GPUs have been designed to be more than simple coprocessors. Many advanced techniques have been applied to improve the GPU computing environment. In the hardware perspective: GPUs are capable of having multiple GPU kernels executed concurrently on their cores; some high-end GPUs have more than one DMA engine on a single GPU board; the rapidly development of dynamically random access memory (DRAM) technology has significantly reduced the cost of large volume of DRAM in modern computers, so using large trunks of nonpageable dedicated physical memory for DMA is feasible. To utilize these hardware features to improve the GPU computing performance, CUDA has implemented and exposed software interfaces for programmers to access them.

CUDA provides the "stream" abstraction, which represents a GPU computing context consisting of a DMA engine for memory copy, and GPU cores for GPU kernel execution. CUDA GPUs support multiple concurrent streams, which essentially enables concurrent execution of multiple GPU kernels on a single GPU, and utilizes multiple DMA engines for concurrently bidirectional PCIe transfers. Each stream is independent of the other: operations (memory copy and GPU kernel execution) in the same stream are sequentially performed, but operations in different streams are totally independent. This provides an

asynchronous streaming GPU computing model, which may fully utilize the execution and copy capabilities of GPUs.

DMA memory copy requires nonpageable memory pages that are locked in physical memory. So if a program wants to copy the data in pageable memory with GPU DMA, the GPU driver has to firstly allocate an extra locked memory buffer, then copy the data from pageable memory to locked memory, and finally copy the data from locked memory to the GPU with DMA. This causes a double-buffering problem that causes an extra copy in host memory and also wastes extra memory space. As a result, a program should use locked memory directly to store its data in order to avoid this double-buffering problem in GPU DMA.

# 2.5 Efficient GPGPU Computing Techniques

To achieve efficient GPGPU computing, the aforementioned GPU features must be considered to design GPU kernels and to design the host side software.

- SIMT architecture requires as few branches as possible in GPU kernel's control flow to avoid warp divergence. This is more an algorithmic requirement than a system one. However, as the packet processing example shows in Section 2.2, sometimes the system-level processing control flow can cause the GPU side divergence, hence it requires the system design to be GPU-aware, to either avoid processing flow divergence, or apply techniques to reduce the divergence overhead like in Snap.

- The wide memory bus requires coalescable memory accesses in consecutive threads.

This not only requires SIMT GPU kernel to guarantee coalescable memory accesses from consecutive threads, but also needs designing coalescing-friendly data structures or data layout in system-level software.

- The variety of different GPU memory requires GPU kernels to be carefully optimized and tuned to make use of the faster read only memory regions and shared memory. This is mostly a general algorithmic requirement, not a very "system" need. But as said in Section 2.3, system code still needs finely tuned system-level algorithms such as Kargus' DFA table placement in texture memory that improves 20% pattern matching performance.

- The CUDA stream technology requires programmers to make use of the concurrency and bidirectional PCIe bus with careful design. This needs system designers to take advantage of concurrent workloads or partitioning large single-threaded workload, properly abstracting the computations on GPUs to utilize the overlapped GPU com-

putation and memory copy pipeline enabled by CUDA stream.

• The page-locked memory requires the programmers to design their memory management mechanism with the consideration of GPU resources at the very beginning. Because memory management in system-level, especially in OS components can be very complex. System components can either have their own memory allocators, or more often, just work as stages in a pipeline that don't own the memory of the processed data buffers at all.

Traditional GPGPU computing considers mostly the GPU side optimization techniques such as the SIMT architecture, wide memory bus and different types of device memory. Their workflows are often very simple, as shown in Section 2.1. For these kind of traditional GPGPU programs, all the complex low-level problems such as memory management, memory copy efficiency, bus bandwidth, device synchronization overhead, interaction with other system components, are hidden and handled efficiently by the system-level code. Now when it comes to the system-level software targeted in this dissertation, all of them must be considered in the system design when integrating GPU computing. Special system-level data usage patterns may cause large PCIe bus bandwidth waste when copying memory, and may also cause difficulty to issue coalescable memory accesses from GPU threads. Using page-locked memory may be not as simple as calling the CUDA memory allocator; it may lead to complex memory page remapping in system code. Some inherently asynchronous system codes may not be able to afford the host-device synchronization because that will change their efficient ways of working. All of these system-level issues must be handled in this dissertation work, as will be shown in the next chapter.

## CHAPTER 3

# SYSTEM-LEVEL GPU COMPUTING PRINCIPLES

A lot of system-level workloads are good candidates of the throughput-oriented GPU accelerations: file systems and storage device layers use encryption, hashing, compression, erasure coding; high bandwidth network traffic processing tasks need routing, forwarding, encryption, error correction coding, intrusion detection, packet classification; a variety of other computing tasks perform virus/malware detection, code verification, program control flow analysis, garbage collection and so on. Not every system-level operation is capable of throughput improvement with GPUs. Those inherently sequential or latency sensitive tasks such as process scheduling, acquiring current date-time, getting process identifier (ID), setting up I/O devices, allocating memory and so on definitely can't afford the relatively high-latency GPU communication that often crosses external buses.

Some early system-level work has demonstrated the amazing performance speedup using GPUs: PacketShader [22], a GPU-accelerated software router, is capable of running IP routing lookup at most 4x faster than the CPU-based mode. SSLShader [23], a GPU-accelerated secure sockets layer (SSL) implementation, runs four times faster than an equivalent CPU version. Gnort [24], as an GPU-accelerated NIDS, has showed 2x speedup over the original CPU-based system. EigenCFA [25], a static program control flow analyzer, has reached as much as 72x speedup when transforming the flow analysis into matrix operations on GPUs.

However, all of them are very specialized systems that have been done in an ad hoc way to deal with performance obstacles such as memory copy overhead, parallel processing design and those mentioned in the previous chapter, without considering any generic systematic design for a wide range of related applications. A general system-level GPU computing model needs to provide generic design principles. It requires a thorough study of system-level behaviors and GPU computing features to identify the common challenges when integrating GPUs into low-level system components, and then come up with generic techniques and

abstractions to decompose the system, trade off design choices according to contexts, and finally solve the problems.

This chapter discusses the generic challenges faced by system-level GPU computing and our proposed design principles. Similar to traditional general purpose GPU computing, tuning GPU kernel to make parallel algorithms fully utilize the SIMT cores is important to system-level code, too. However, a unique feature of system-level computing tasks is that most of them are much simpler than the application-level tasks in scientific computing and graphics processing. If we take a look at the surveyed computing tasks in system-level in Section 6.1, they are mostly one-round deterministic algorithms without any iterative scheme and convergence requirement such as in partial differential equation (PDE) algorithms and randomized simulations. In that case, other noncomputational costs may become major overhead: for example, as we evaluated for GPUstore, the significant AES performance improvements with a variety of memory copy optimization techniques show that the memory copy, rather than the cipher computation, is the bottleneck. As a result, system-level GPU computing is faced with challenges from not only traditional device side GPU kernel optimization, but also the host side GPU computing related elements. The following sections discuss each of the major challenges we've identified in the GPUstore and Snap projects and the generic techniques to deal with them.

# 3.1 Throughput-oriented Architecture

The SIMT GPU architecture enables simple but highly parallel computing for large throughput processing. But the SIMT architecture is also a big challenge to GPU kernel design and GPU computing workload. As for the GPU kernel design, it means avoiding control flow divergence via tuned GPU code or SIMT-friendly data structures to process. To fit the SIMT architecture, the workload must be able to provide enough parallelism to fully utilize the thousands of parallel SIMT cores. The parallelism may come from the parallelized algorithms in terms of GPU kernels. More importantly, it comes from the amount of data to be processed in one shot, which often requires batched processing in system environments. When trying to provide a generic design for a variety of system-level applications, a right workload abstraction that covers the various processing tasks is needed to guarantee the parallelism, and also to make it easy to design divergenceless GPU kernels.

#### 3.1.1 Parallel Workload Abstraction

Considering the thousands of cores on a modern GPU that processes one basic data unit in one thread, at least the same number of basic units is required to fully utilize all the cores. This is actually the key to achieve high throughput in GPU computing. Taking the GTX Titan Black [3] as an example: even with the parallelized AES algorithm that uses four threads to process a single 16-byte block, its 2880 cores still need  $2880 \times 4 = 11KB$  data to process in one GPU kernel launch. If we consider the context switching due to global memory access, even more data are required to keep GPU cores busy.

Unfortunately, system-level software is often designed to process data sequentially due to the latency-oriented system design philosophy through the ages. However, the performance of parallel and sequential processors have been significantly improved to be easily achieve very low latency, and also today's "big data" workloads focus more on high throughput processing, even at the system-level. Batching is a simple yet effective technique to accumulate enough parallelism in one-shot workload. Instead of a single data unit to be processed at one time, a one-shot workload with batching now includes enough units to fully occupy the thousands of GPU cores. "Enough" is ambiguous in the high-level workload abstraction. An intuitive but effective policy for concrete design is to ensure that processing the batched workload on GPUs is at least faster than on CPUs.

An obvious drawback of batching is the increased latency. This may cause a serious performance problem in some latency sensitive software, especially the network applications such as video conference, video streaming, etc. As we will see in Snap, the packet processing latency introduced by batching is eight to nine times larger than the nonbatching latency. So batching is not a pervasive solution to adapt sequential software with the parallel GPUs. This also reveals the fact that not every system-level software can benefit from parallel GPUs, such as those latency sensitive computing tasks whose algorithms can't be efficiently parallelized.

## 3.1.2 Avoid Control Flow Divergence

Many research projects [26, 27, 28, 29, 30, 31, 32] have been focused on designing efficient SIMT style parallel implementation of particular algorithms on the GPU. Besides those well-studied techniques, how to efficiently partition the workload into SIMT threads and how to choose SIMT-friendly algorithms and data structures (if possible) are also very important.

The workload partitioning is often very straightforward: each GPU thread processes one single basic data unit. Many system-level computing tasks can use such simple partitioning scheme such as computing erasure code of one disk sector per thread, encrypting a single sixteen-byte AES block per thread, looking up next hop for one IP address per thread, etc. However, exceptions always exist. The AES algorithm is an example, which has been

parallelized by exploiting the intrablock parallelism [33]. GPUstore applied this technique in its AES implementation to have four threads to encrypt/decrypt a single AES block.

Designing the data structures used by processing logic to make them SIMT-friendly is another technique to avoid control flow divergence. One example is the pattern matching algorithm in Snap that is based on DFA. The DFA matching is a very simple loop: get the current symbol; find the next state indexed by the symbol in current state's transition table; use the found state as the current state. The algorithm itself can be implemented in SIMT style because all input strings use the same three-step matching. But for the second step, some transition table data structures cannot ensure same code execution when finding the next state. For example, a tree-based map may need different lookup steps for different symbols to find the mapped states, which means different GPU threads may have to execute different numbers of lookup loops to find the next states, and hence is not SIMT-friendly. In the meanwhile, an array-based transition table, which assigns state for every symbol in the DFA alphabet, can guarantee equal steps to find the next state of any given symbol, and hence is SIMT-friendly. That's because we can use the symbol as the array index to fetch the mapped state, and one state lookup becomes a single array access. So although the tree-based map is more memory-efficient and the array-based map is very memory-consuming because even invalid symbols in the alphabet have transition states, sometimes the memory may be sacrificed to achieve SIMT-friendly GPU code.

#### 3.1.2.1 When It Is Unavoidable

An effective but not efficient way that can always solve the control flow divergence is to partition the computing tasks into multiple GPU kernels, each GPU kernel works for a particular control flow branch of the computing task. This needs some information available at the host side to indicate how many threads a GPU kernel should be executed by, and which data items should be processed by a particular GPU kernel. Such host side information implies a device-to-host memory copy, the necessary host-device synchronization for its completion and probably a data structure reorganization, which may cost more than admitting divergence at the GPU side. So it is not always unacceptable to introduce divergence into a GPU kernel. The batched packet processing in different GPU elements in Snap is a very representative example.

However, allowing divergence in GPU kernel doesn't mean writing arbitrary code; we still need to minimize the effects. We have proposed and implemented the predicated execution to minimize the divergence affections. More details of the predicated execution are in Section 5.3.2.

# 3.2 Coalesce Global Memory Accesses

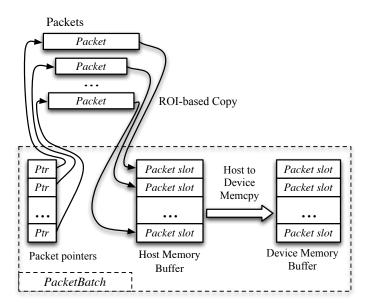

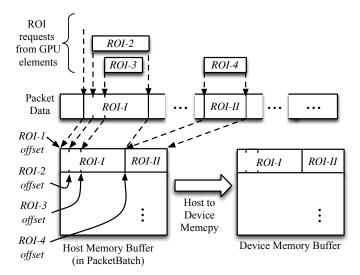

The throughput-oriented GPU architecture is armed with not only high computation throughput, but also high memory access throughput. To fully utilize the 384 bits global memory bus in GTX Titan Black [3], coalescable memory accesses must be issued from neighbor threads in a thread block. Compared with noncoalesced access, coalesced memory access can achieve orders of magnitude faster [26]. So the GPU kernel must be designed to access consecutive memory locations from threads within the same thread block or warp. Besides the GPU kernel code, the data structures to be processed must be carefully organized to make them coalescing-friendly. Some kinds of workloads are quite easy to satisfy the coalescing requirement, for example, data read from a block device are naturally consecutively stored, hence when encrypting them, neighbor GPU threads can always coalesce their memory accesses. However, some workloads are not that coalescing-friendly, needing a coalescing-aware abstraction to achieve a generic solution. A simple but very good example is the IP routing lookup. The lookup GPU kernel needs only the destination IP address of a packet. If we put the entire packet into the global memory for each thread to access, the memory reads for IP addresses issued from neighbor threads will be scattered. One 384 bits memory transaction may only read 32 bits effective data, which wastes more than 90% memory bandwidth. But if we organize the destination IP addresses into a separate buffer, then up to 12 memory reads for the IP addresses issued from neighbor threads can be coalesced into a single memory transaction, which significantly reduces the number of global memory transactions. The "region-of-interest"-based (ROI) slicing technique applied in Snap is an effective abstraction of the workload data to build such coalescing-friendly data structures for a variety of GPU-accelerated computating tasks (see Chapter 5).

# 3.3 Overlapped GPU Operations

The typical GPU computing workflow mentioned in Section 2.1 can be pipelined to improve the utilization of the two major GPU components: SIMT cores and DMA engines. The pipelined model needs multiple CUDA streams, each of which carries proper-size workloads for certain computing tasks. This may require the workload to be split into multiple trunks in order to fill into multiple streams. The host code will be responsible to do such workload splitting, which needs the task-specific knowledge to ensure the splitting is correct. For a generic GPU computing framework such as GPUstore, it is impractical to put those splitting knowledge of every task into the generic framework. The computing tasks

need a right abstraction to describe both the task-specific logic and the task management (such as partitioning) logic. For example, GPUstore provides the modular GPU services, which are the abstraction of computing tasks. Each GPU service not only processes computing requests issued from GPUstore clients, but also does service-specific request scheduling including workload splitting and merging.

This requirement seems totally contrast to the parallelism one in Section 3.1.1. However, it is not a paradox. An application usually needs to find the balance point of these two requirements to decide the optimal size of the workload to be processed on GPUs in one shot, so as to achieve the best performance. This can be done either dynamically or statically. A static approach finds the balance point offline by benchmarking the computing tasks and uses predefined sizes at run time. Both GPUstore and Snap simply use this approach in their prototypes. The dynamic way would do microbenchmarking at run time to find optimal sizes for the specific execution hardware and software environment. It can adjust workload sizes according to the hardware and system load, and hence is more accurate.

# 3.4 Asynchronous GPU Programming

CUDA stream requires asynchronous DMA memory copy and GPU kernel launching operations so that a single CPU thread can launch multiple streams. However, current GPU programming model needs the synchronization between the host and the device to detect the completion of the device operations in each stream. This may not be a problem at all for traditional GPGPU computing that just focuses on a particular computing task. However, many system-level components are designed to exploit asynchrony in order to achieve high performance.

For example, filesystems work with the virtual file system (VFS) layer, and often rely on the OS kernel page-cache for reading and writing. By its nature, the page-cache makes all I/O operations asynchronous: read and write requests to the page cache are not synchronous unless an explicit sync operation is called or a sync flag is set when opening a file.

Other examples include the virtual block device drivers, which work with the OS kernel's block I/O layer. This layer is an asynchronous request processing system. Once submitted, block I/O requests are maintained in queues. Device drivers, such as small computer system interface (SCSI) drivers, are responsible for processing the queue and invoking callbacks when the I/O is complete.

Some filesystems and block devices, such as network file system (NFS), common Internet file system (CIFS), and iSCSI (Internet SCSI), depend on the network stack to provide their

functionality. Because of the high and unpredictable latency on a network, these subsystems are asynchronous by necessity.

When it goes to the network packet processing, it is totally asynchronous workflow. Although there does exist totally synchronous network stacks such as the uIP [34] and lwIP [35], they are designed for memory constraint embedded systems, not for performance. As a result, the synchronization CUDA call is totally unacceptable in those asynchronous environment because it will block the normal workflow and may cause performance slow down.

GPUstore and Snap solve this problem by implementing asynchronous CUDA stream callback mechanism to enable completely asynchronous GPU program control flow. Such callback mechanism can be implemented in two different approaches.

**Polling-based.** this method has a thread keep polling stream state change and invoke callbacks. It is obvious that this approach can get low latency response but will keep a CPU core in busy waiting loop.

**Signal-based.** this is implemented with the events invoked by GPU interrupts at the low level. The signal-based response latency is definitely higher than the polling-based one, but its advantage is also obvious: CPU cores can be freed to process other work without busy waiting.

At the time of writing this dissertation, the latest CUDA release has provided similar signal-based callback for streams after GPUstore did that for more than two years. This further confirms the effectiveness of the techniques we've proposed.

# 3.5 Reduce Memory Copy Overhead

Having said at the beginning of this chapter, the memory copy is often the major overhead compared with the computation. Many different aspects are related to the performance of memory copy. Since we are discussing system-level GPU computing, the memory copy is not only the DMA over PCIe bus. We also need to consider what happens in the host main memory as an entire system. We will start from the obvious challenges and problems in GPU related memory copy, then gradually introduce other vital issues and techniques to deal with them.

#### 3.5.1 DMA Overhead

The overhead of DMA comes from its special requirement: the memory pages in main memory must not be swapped out (paging) during DMA. To satisfy such requirement when copying data in pageable memory to GPUs, CUDA GPU drivers use the aforementioned double-buffering approach as described in Section 2.4. According to the evaluations [36], double-buffering DMA can be two times slower than using page-locked memory directly. Compared with pageable memory, using page-locked memory may lock too many physical pages and reduce the available memory for other applications. However, considering today's cheap DRAM and widely available tens of gigabytes DRAM on a single machine, locking even 6GB memory (for a high end GPU [3]) is totally acceptable.

## 3.5.2 Avoid Double-buffering

The aforementioned solution with CUDA page-locked memory requires the system code to use CUDA-allocated memory as its data buffer. This seems trivial: traditional GPGPU computing usually reads the data from a file or the network into host memory, copies the entire data buffer into GPU device memory, and does the computation. It is seldom that the host memory used in this scenario may have any other users or complicated dependencies, so it is easy to replace it with CUDA-allocated page-locked memory. However, the code in a system component often works as a stage of a long data processing pipeline. In that case, it may be impractical to modify the entire system from the beginning of the pipeline to use CUDA's memory, especially in a large complex system such as the operating system kernel. One way to deal with this is allocating a separate page-locked buffer with CUDA, and copy the data to be processed into this CUDA buffer before DMA (and similar approach for the processing result). This leads to double-buffering, which is similar to the aforementioned early stage CUDA DMA implementation for pageable memory: introducing extra copy in host memory. To avoid the double-buffering problem, we've proposed and implemented the page remapping technique, which can remap external page-locked memory pages into CUDA GPU driver's memory area, and make them DMA-capable just like CUDA page-locked memory (refer to Section 4.1.2.) This allows minimum invasive GPU computing integration into an existing complex system: only the component containing the computing tasks needs a few modifications.

There do exist some special cases where the component we'd like to put GPU-accelerated computing tasks into may be the beginning of the data processing pipeline. It may also be a pipeline stage that allocates memory for later use. In those cases, replacing previous malloc or similar memory allocators with CUDA's memory allocation functions is feasible and efficient. Introducing remapping in those cases doesn't make any sense due to the added complexity of the extra page mappings.

The techniques in this section try to avoid memory copy in host memory because such copy is not necessary. However, there is an implicit assumption that the data in the memory

buffer are all useful to the computation. Otherwise it may be unwise to copy the entire buffer to device since it wastes the relatively slow PCIe bandwidth, as we shall discuss in the following section.

#### 3.5.3 Trade Off Memory Copy Costs

Some computing tasks in a system component may need only small pieces of a large data unit it receives. Typical examples are the packet processing tasks: IP routing just needs the destination IP address, layer 2 forwarding just needs the destination's media access control (MAC) address, packet classification just needs five small fields, etc. Copying the entire data unit into GPU memory can waste a large portion of the PCIe bus bandwidth: considering the 4 bytes IP address versus the minimum 64 bytes packet. At the same time, the host side memory bandwidth is much faster than the PCIe bus. Take a look at the machine I used for Snap evaluation: the main memory has a 38.4GB/s bandwidth, while the maximum throughput of the PCIe 2.0 16x slot is 8GB/s in each direction, which is a 4.8 times difference. As a result, for computing tasks with the data usage patterns discussed here, copying the needed data pieces into a much smaller page-locked memory buffer and then launching a PCIe DMA for this small buffer may lead to a much faster total memory copy than copying the entire data unit into GPU memory through PCIe bus. The aforementioned Snap's the ROI-based slicing technique is based on this idea. It takes advantage of the much faster host memory to achieve fast host-device memory copy. As we mentioned in Section 3.2, it also makes coalescing-friendly data structures for GPUs (refer to Chapter 5 for details).

#### 3.5.4 Discussion

Section 3.5.3 advocates a technique that is totally opposite to the one in its previous section (Section 3.5.2). But they are not paradoxical. It is the data usage pattern of the computing task that decides which technique to use. On the one hand, for a computing task that needs the entire data unit received by the enclosing system for its computation, it should avoid extra buffers in host memory for the same data unit content with either the remapping technique or using CUDA page-locked memory directly, depending on the memory management role of the system as we discussed in Section 3.5.2. On the other hand, a computing task needing only small pieces of the entire data unit should trade off the main memory bandwidth and the host-device memory copy bandwidth, and may use techniques similar to Snap's ROI-based slicing for faster total memory copy performance. Snap's ROI-based slicing is a very flexible data abstraction to deal with both kinds of usage

patterns: it allows computing tasks to define their own pieces to be processed in a single data unit, for a "use all" usage pattern, the computing task can specify the entire data unit as its interested region.

# 3.6 Miscellaneous Challenges

There are some challenges caused by the limitations in current GPU computing libraries or GPU hardware. Though we can believe that with the development of GPU technology and the GPU market, these obstacles may disappear in future, it is still worth describing them here for readers who are trying to apply GPU computing into system components at this time. The challenges discussed in this section are only related to our GPU computing experiences learned from GPUstore and Snap, the survey chapter (in Chapter 6) discusses more such challenges and solutions provided by other system-level GPU computing works.

#### 3.6.1 Kernel-User Communication

Currently, in almost all GPU computing libraries, drivers are closed source, not to mention the even more closed GPU hardware. This leads to a big performance problem when applying GPU computing into an operating system: the OS kernel mode code has to rely on the userspace GPU computing library to use GPUs. So now in OS kernel mode, using GPUs is not as efficient as a function call in userspace, but a cross context communication. Such a system needs an efficient kernel-user communication mechanism for invoking GPU computing library functions, and also memory sharing between two modes for computing data. GPUstore got this problem on Linux kernel when using CUDA GPU library. Current open source GPU drivers such as nouvea [37] and open source CUDA implementation such as Gdev [38] still can't reach the proprietary software's performance. GPUstore uses a userspace helper to deal with requests from OS kernel and invoke CUDA calls. The userspace helper is based on polling-based file event mechanism to achieve fast kernel-user communication. The details are in Chapter 4. The Barracuda [39] GPU microdriver has evaluated different approaches to implement efficient kernel-user communication for GPU computing.

#### 3.6.2 Implicit Synchronization

The host-device synchronization happens not only when the host side explicitly calls cudaDeviceSynchronize function, but also when some GPU resource management operations are performed [4]. Such operations include CUDA host or device memory allocation, GPU information query, etc. The host and device memory allocation is the main trouble

maker because it is almost unavoidable. This may stall the aforementioned asynchronous GPU programming in Section 3.4 even when there is no explicit stream synchronization. As a result, as we will see in Chapter 6, a common technique used by many system-level GPU computing works including our GPUstore and Snap frameworks is to preallocate CUDA page-locked memory, and manage the memory allocation on their own. This can easily consume a lot of memory, but due to the current GPU limitations, it is a must to achieve asynchronous GPU computing.

# 3.7 Summary

In this chapter, we discussed generic system-level challenges and also proposed high-level principles and techniques to deal with them. The proposed principles and techniques are designed to make system code efficiently work with the throughput-oriented GPU architecture, take advantage of the wide GPU memory interface, do nonblocking host and device communication and reduce unnecessary overheads during GPU DMA. These principles are mainly about batching to provide parallel workloads, truly asynchronously programming GPUs with callbacks or status polling at the CPU side, compacting workload data to reduce unnecessary PCIe transfer, and using locked memory directly to avoid double-buffering DMA. In the next two chapters, we will discuss our two concrete frameworks: GPUstore and Snap, to explain how we apply these generic principles and techniques in practice to deal with their specific problems.

## CHAPTER 4

# GPUstore: GPU COMPUTING FOR STORAGE

This chapter covers the design, implementation and evaluation of GPUstore. GPUstore is a framework for integrating GPU computing into storage systems in Linux kernel. Different from the systems surveyed in Section 6.1.2, GPUstore is a generic framework, not for a particular storage application or subsystem. It has been designed to collaborate with the storage subsystem in Linux kernel in order to use the GPU as a coprocessor. We try to minimize the source code change for a storage component to use GPU computing. So GPUstore follows the OS working style and utilizes existing resource management mechanisms to avoid any fundamental change in the OS kernel. GPUstore has been evaluated with three storage system case studies, showing its efficiency and effectiveness.

# 4.1 Design

This section will go into the details of how GPUstore has been designed to apply the generic technical principles discussed in Chapter 3 in practice. The following text first takes an overview of the architecture, then discusses specific aspects including memory management, request scheduling and stream management.

#### 4.1.1 Overview

GPUstore has three main functional blocks: memory management, request management and streams management, as shown in Figure 4.1. There are also GPU "services" that don't belong to the framework, but are managed by GPUstore and essential to provide GPU computing tasks. GPUstore abstracts the computing tasks into "services." So storage components request for services to get computational functionalities. Services are modular libraries that are dynamically linked with GPUstore. There is a generic service interface provided by GPUstore to use and manage concrete services. Due to the closed source GPU driver and library, GPUstore has to use a userspace helper to interact with the userspace

Figure 4.1. The architecture of GPUstore.